FPGA+MCU实现VGA图象信号发生器

时钟频率:25.175MHz(像素输出的频率)

行频: 31469Hz

场频: 59.94Hz(每秒图像刷新频率)

图象信号显示的颜色种类与表示R、G、B三基色的二进制数位数有关,表1列出了8种颜色的编码方式。

4、系统设计

4.1 图像信号产生模块的设计

产生图像信号的核心器件采用Altera公司的Cyclone FPGA芯片EP1C3T144C8N。它具有多达20060个逻辑单元。最大用户I/O数 104个。器件中M4K存储块提供288kbit存储容量,能够被配置来支持多种操作模式,包括RAM、ROM、FIFO及单口和双口模式。

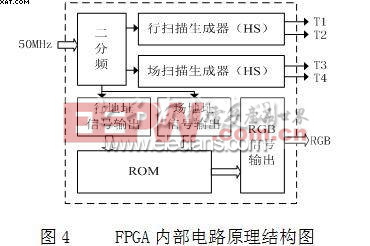

Cyclone器件具有高级外部存储器接口,允许设计者将外部单数据率(SDR)SDRAM,双数据率(DDR)、SDRAM和 DDR FCRAM 器件集成到复杂系统设计中,而不会降低数据访问的性能。并且还具有两个可编程锁相环(PLL)和八个全局时钟线,能提供时钟管理和频率合成,实现最大的系统功能。根据VGA显示原理,图象信号产生器的主要功能是:产生时序驱动信号HS、VS及VGA彩色图象编码信号,同时在正确的时序控制下,输出ROM中的象素数据至显示器的VGA接口,进行图象显示。FPGA内部电路原理结构如图4。本文利用Altera公司QuartusⅡ6.0开发平台,遵循自顶向下的设计方法,针对各功能模块,采用VHDL语言对FPGA器件编程,产生HS和VS扫描时序信号及各种图象信号。

VGA时序信号是图象显示的关键,行场扫描时序的产生,是利用逻辑编程的方法实现的,即用VHDL编写分频器,计时器模块,来获得T1、T2、T3、T4时序。当输出数字、彩条信号和棋盘格图象时,由外部12M有源晶振提供时钟输入,其中行频HS:12MHZ ÷13÷29=31830Hz、场频VS:31830Hz÷480×0.93=61.67Hz、T1=1/31830Hz×4/29=25.96us、T2=1/31830Hz×5/29=6.04us、T3为两个行周期(T1+T2),T4为480个行周期。

图象信号包括数字、彩条、棋盘格,和ROM中定制的图形等。数字信号和彩条信号的产生是按行场方向将屏幕各进行8等分,相当于一个8×8的点阵,在对应位置显示相应颜色即可获得所需图像信号;棋盘格信号是将横彩条和竖彩条相异或获得。ROM中定制的较为复杂的彩色图像,需采用像素点输出,即将图像各像素点的信息存储于ROM中,再以一定的频率输出。FPGA器件ROM的定制有两种方法:第一种方法是利用FPGA器件的嵌入式存储器定制LPM_ROM,用.MIF文件或.HEX文件对其进行初始化,这种方法获得的ROM最大寻址空间为2 12,可以存储一幅分辨率为64×64的图像信息;第二种方法是在FPGA逻辑资源的限度内用VHDL语言定制一个ROM,采用CASE语句对其进行初始化,这种方法获得的ROM在存储深度较大时,编译时对时间的开销较大。ROM初始化完成后,在25MHz的时钟频率下输出存储的图像信息。其图象颜色种类的多少取决于存储空间的大小。

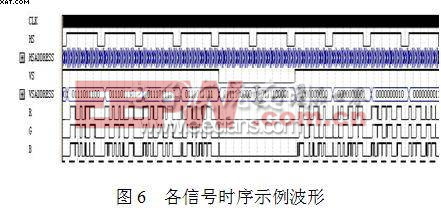

ROM定制的图象信息是利用FPGA嵌入的存储器定制LPM_ROM,可以用于存储一幅64×64分辨率的图像信息,数据线宽为3位,地址线12根,采用组合寻址方式,即行地址HSADDRESS占低6位,场地址VSADDRESS占高6位;若要显示更为复杂的图象信息,只需扩展存储器及寻址的数据线宽度,为了保证行地址信号输出与行扫描信号输出同步,场地址信号输出与场扫描信号输出同步,在VHDL编程时,可用25MHz时钟作为进程的启动信号。输出信号的时序波形如图6所示。各种图象信号的输出是由数据选择器通过VHDL编程实现的。

评论