GPS信号中断时惯导芯片的位置信息感知系统设计

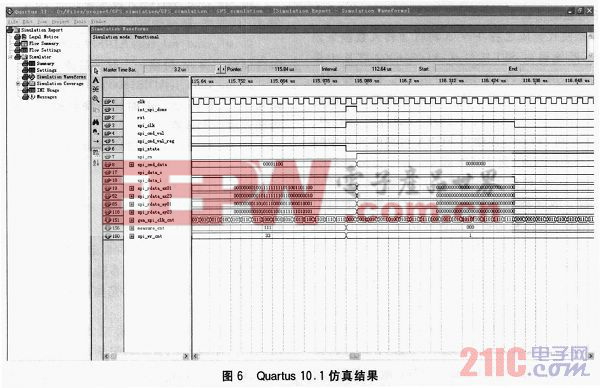

3.2 软件功能仿真

本系统的底层SPI通信部分使用FPGA进行驱动,采用Verilog HDL语言编写程序,并在Quartus 10.1集成环境下进行功能仿真验证,如图6所示。结果显示,数据采集符合设计逻辑,当所有数据采集完成一次之后立即送出中断信号触发DSP读取。本文引用地址:http://www.eepw.com.cn/article/150076.htm

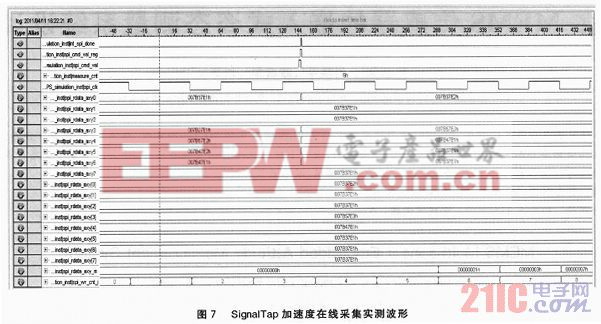

4 测试结果

利用Signal Tap II Logic Analyzer在线逻辑分析仪进行板上硬件实际调试,图7为SignalTap加速度在线采集实测波形。测试结果显示数据采集和处理符合芯片时序要求;FPGA与DSP的EMIF接口配合良好,经过后续DSP软件算法处理后能成功推算出移动物体当前的GPS信息,及时上报CPU(每秒1 s)。其中SPI总线通信时钟为1.4 MHz。经过测试,系统完全能够达到设计要求,已在某大型通信系统中得到应用。

结语

通过本系统的设计和调试过程可以看出,使用FPGA作为物理层驱动具有SPI接口的数字芯片是简单而有效的一种数字设计方案,可以较容易地满足芯片的时序要求。通过与EMIF接口的配合还可以很好地利用DSP芯片完成众多嵌入式系统的设计。

评论