基于FPGA的嵌入式系统USB接口设计

摘要:设计基于FPGA的IP-BX电话应用系统,用于传统的电话网络(PSTN)与PC机之间的接口连接。USB2.0接口器件EZ-USB FX2 CY7C68013A-56工作在slave FIFO模式,为基于FPGA的嵌入式系统与PC机之间提供数据和命令通道,从而可满足PC机与FPGA之间数据与命令的高速传输,实现PSTN与PC机之间的电话通信。硬件调试结果表明系统工作稳定,通话质量满足要求。

本文引用地址:http://www.eepw.com.cn/article/149804.htm通用串行总线USB(Universal Serial Bus)是应用于PC领域的接口技术,已得到广泛应用。USB2.0已成为目前电脑中的标准扩展接口。本系统设计的目的在于为公共交换电话网络(PSTN)和PC机之间提供一个数字接口,设计中PC机是主机,基于FPGA的嵌入式系统是USB设备。该系统是IP-PBX的简化系统,大量工作由PC的服务器完成,而这里重点介绍以FPGA为控制核心的USB接口设计。

1 系统结构设计

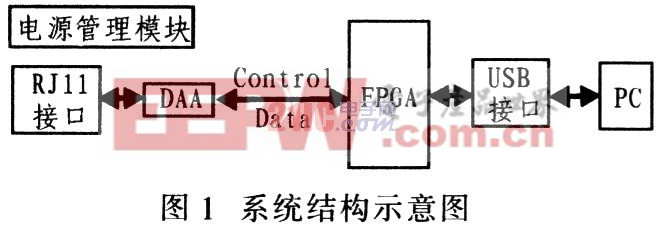

该系统通过TRM(Telephone Response Module)和PC服务器实现PSTN网络和Internet网络之间自由、高效通话。图l为整个系统结构示意图。

系统工作过程:当有来电时,DAA向FPGA申请中断。FPGA收到中断后,使用USB的中断传输向主机报告有外接来电,则PC的应用软件会提示用户选择摘机或拒绝。摘机后,FPGA在接收到命令后就会接通电话,然后语音数据通过USB的同步传输进行双向传送。当用户向外拨号时,其过程与来电时的情况是相同的。

2 系统硬件模块设计

2.1系统硬件框图

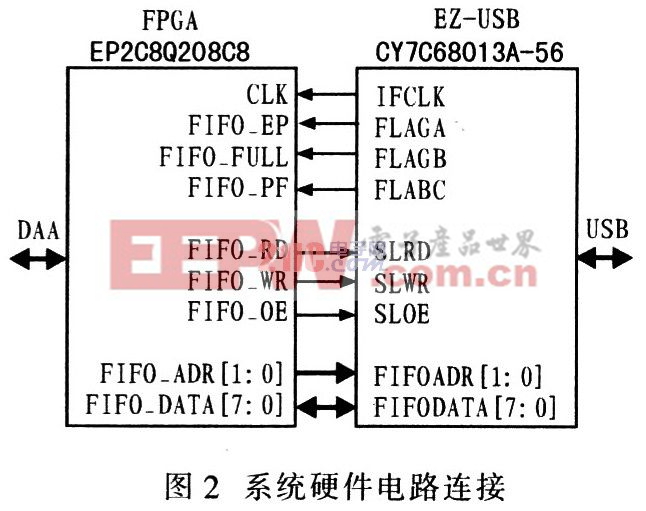

本设计采用FPGA作为核心控制器件,其控制对象是USB2.0接口器件EZ-USB FX2 CY7C68013A-56。图2为EZ-USB器件工作在Slave FIFO模式下时FX2 USB和FPGA的典型电路连接图。

2.2 FPGA和USB简介

设计中的核心控制器件FPGA选用Ahrea公司的EP2C8Q208C8,而USB设备器件则选用Cypress公司的CY7C68013A-56。EP2C8Q208C8是Ahera Cyclone II系列器件中的一种,Cyclone II FPGA是基于Stratix II的90 nm工艺生产的低成本FPGA。Cyclone II FPGA的应用主要定位在终端市场,如消费类电子、计算机、工业和汽车等领域。EP2C8Q208C8内部有2个锁相环(PLL)和8个全局时钟网络,8 256个逻辑单元(LE)个,36个M4K RAM,18个乘法器模块,可用I/O数138个。EP2C8Q208C8具有低成本、高性能、低功耗和对IP-PBX系统的可扩展性(足够多的I/O接口)的优点,因此这里选择该器件作为系统的控制器件。

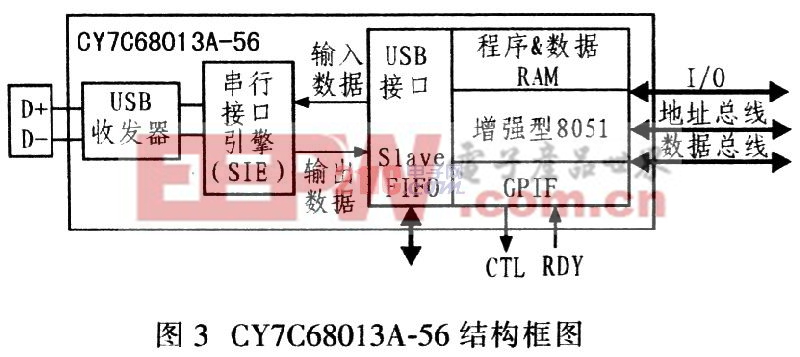

CY7C68013A-56器件是第1个包含USB2.0的集成微控制器,其内部集成有1个增强型的8051,1个智能USB串行接口引擎(SIE),1个USB数据收发器,3个8位。I/O、16位地址线、8.5 KB RAM和4 KB的FIFO等。增强型8051内核完全与标准805l兼容,而性能可达到标准805l的3倍以上。图3为CY7C68013A-56的结构框图。

CY7C68013A器件在数据传输时利用4 KB的FIFO,包含7个端点:EPOIN/OUT,EPlIN,EPlOUT,EP2,EP4,EP6,EP8。其中EPO、EPIIN和EPlOUT是3个64 B的缓冲端点,只能被固件访问,EP0是默认的数据输入输出端口缓存,默认工作于控制传输,EPlIN和EPlOUT是独立的64 B缓存,可以配置成块传输、中断传输或同步传输。端点2、4、6、8是大容量高宽带的数据传输端点,可配置为各种带宽以满足实际需求。端点2、6能配置成每帧成512 B或l 024 B,并可配置为2、3、4级,则EP2,EP6最大能被配置为4 KB的缓存;端点4、8则能配置为每帧512 B的缓存。

3 系统软件设计

3.1 USB Firmware设计

由于设计中使用FPGA控制USB设备进行语音电话通信,所以在USB部分使用3种USB传输模式:控制传输、中断传输、等时传输。控制传输用于实现设备枚举主机的标准请求以及厂商自定义请求;中断传输用于实现设备对主机的唤醒,是唯一的设备主动向主机发送数据的传输方式;等时传输用于实现语音数据的双向同步传输。USB Firmware设计重点是语音的通信段。

CY7C68013A具有PORTS、Slave FIFO、GPlF共3种工作模式。PORTS模式是最基本的数据传输方式,其数据传输需CPU直接参与,适于传输速率要求不高的场合;GPIF模式是主机方式,内部主机控制端点FIFO;Slave FIFO模式是从机方式,外部控制器,如FPGA、DSP。应用中使用异步FIFO方式,采用内部48 MHz时钟,自动方式,而固件程序的编写则以Cypress公司提供的固件程序框架为基础,在其初始化函数中添加自己的配置代码。

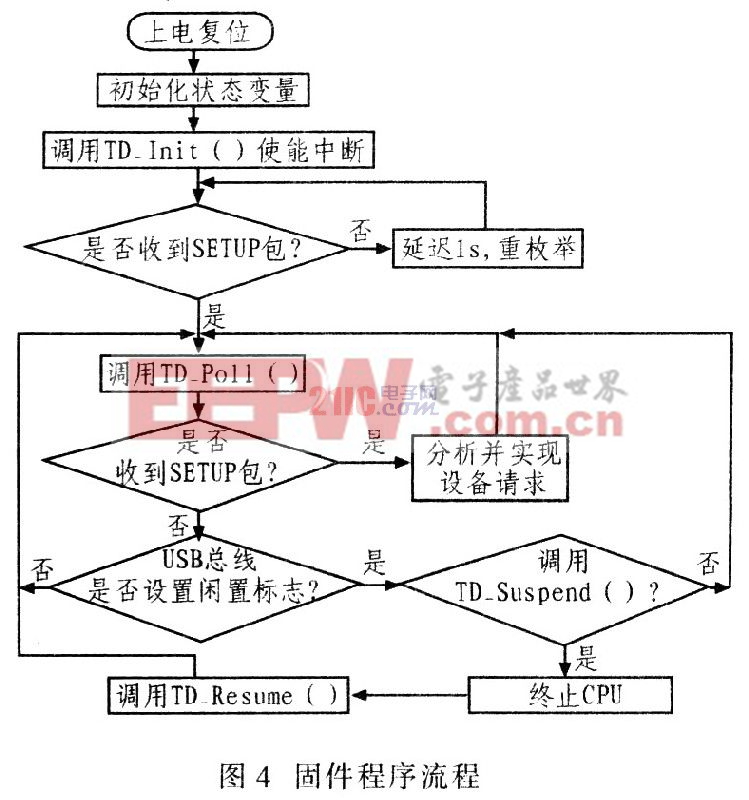

在整个系统中,CY7C68013A的固件主要完成以下工作:初始化USB器件;作为USB接口与主机通信并传输数据;利用CY7C68013A器件的Slave FlFO接口控制USB器件和外部控制器之间的数据传输。因此同件主程序比较复杂,除了上面的TD_lnit()初始化外,还需要大量函数,但基本结构相对简单,包括3个过程:USB控制器的初始化;主函数,包括处理标准设备请求的代码;中断处理,包括处理各种中断的程序代码。图4为同件主程序流程。

评论