基于ARM双内核的平台化网络产品设计

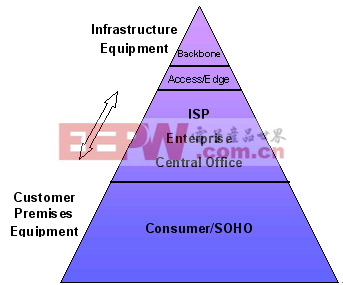

新兴的无线连接技术促使更多产品向新一代商务及家庭网络应用方向发展。因此,网络市场中的用户终端设备(CPE:customer premises equipment)部分,也正朝着消费市场的状态转变。

CPE产品的成功,需要由一个设计平台及灵活的产品开发流程来支撑,以满足各种新兴网络协议的性能需求,加快研发进程,最终提供经济而节能的终端产品。

图1网络市场中设备数量分布

技术发展动力

对网络设备而言,日益增长的带宽需求是最为显著的技术发展动力。曾有人指出带宽正以类似于摩尔定律的方式增长,如:客户端的带宽每18-24个月增加一倍,而核心/光纤带宽约每8月增长一倍[2]。

然而,日益增长的带宽需求并不是唯一促进技术发展的原因。对CPE的功能及智能性需求的增长也是另一种驱动因素,因此,单单采用更大更快的处理器并不是最为有效的方案。

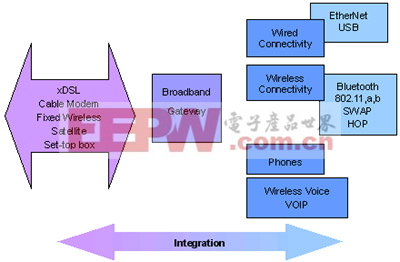

更多功能的集成、增强的安全性和多种协议的发展等都将使CPE产品越来越复杂。不同协议的交换处理是众多CPE应用产品的普遍需求。如:无线局域网接口设备中的核心功能是在以太网和多种IEEE802.11接口标准间进行转换。产品需求中可能会需要接口设备能够提供多种接入点,以支持管理多种格式数据流的需求。

即使网络产品不是便携式的,低功耗也非常重要。低功耗设计可以降低对外壳及印刷电路板(PCB)制造的限制,也无需电扇散热。除去了这些问题,设计的可靠也将大大提高。

图2将各类产品集中使用的思路促使应用产品往集成化方向发展

为了达到优良的实时性能,处理器应能有效地管理中断,并同时具备足够的数据处理能力。上下文的切换也是关键的需求,具有在中断服务程序和任务模式编码之间有效切换的能力会带来更佳的性能。当然,还应尽量减少中断服务和进行上下文切换的延时。

这类产品中的存储器管理是个需要仔细考虑的问题。完全的嵌入式系统通常运行在固定的程序集中,无需加入新的程序。这样的应用产品并不需要带有地址转换的完整存储器管理单元(MMU)。更简单的存储器保护单元(MPU)通常可以高效地运行实时操作系统(RTOS),允许多程序运行,进行上下文切换时开销更少。含有 MMU的内核进行中断服务时可能比基于MPU的内核要低效一些,同时还需要为地址转换设置更大的外部存储器。

CPE产品正朝着家用消费品市场进军。目前,市场竞争激烈,终端设备的价格便成为主要的竞争优势。同样地,缩短产品上市时间,也是提高市场占有率的重要优势。客制化终端网络设备将真正缩短推出系列产品的上市时间。市场需要一种既能节约开发费用,又能缩短研发时间,并且能简便地开发系列产品的技术方案。

无论从商务或技术角度出发考察一个片上系统,都需要处理器方案能满足多种网络应中的特殊控制和信号处理需求。设计的技术需求表明,若处理器性能远远高于实际需求,即设计了太多不需要的功能,意味着将无端地增加产品成本;但一定的性能冗余和灵活性可以支持产品的后续发展,而无需进行更本性的重新设计。

总结上述两个驱动因素,开发人员应能够从技术和商业两方面来衡量实现一个具体设备。

ARM在网络设备中的应用

为了增加带宽并拥有更复杂的协议数据交换能力,许多设计人员正考虑在设计中使用双核。

CPE系统需要满足多重的复杂控制需求。许多系统体系结构建立于单内核基础上,管理高级别的功能,如进行系统配置操作和运行实时操作系统,而后与专用的状态机集成,进行如数据包处理等操作。然而,这样做使得设计和调试非常复杂,特别是设计含有多重私有状态机时。

嵌入式软件技术方案相较于复杂的私有硬件技术方案更易维护和推广运用。嵌入式软件技术方案能使用高级语言进行编程,使用众所周知的程序员模式,并拥有大量具有丰富经验的工程师作为后盾。

ASIC的集成度已经非常高,因而,CPU内核的面积非常小。用第二个或第三个处理器来代替以往用多重的独立硬件模块显得更加经济和实际。

在此种趋势的推动下,ARM推出了集成了双ARM946E-S微处理器内核的PrimeXsys双内核平台(946DCP)。

ARM946E-S特点

ARM946E-S内含有ARM9E-S?内核,为运行实时操作系统的嵌入式产品提供指令(I)、数据(D)高速缓存、紧密耦合存储器(TCM)、写缓冲器、存储器保护单元(MPU)。指令和数据缓存和TCM缓存都是可配置的。存储器体系结构令设计者可依据实际情况调整缓存和TCM大小。

ARM9E-S微处理体系结构提供了快速中断响应和上下文切换功能。该体系结构非常合适用于如Wind River的VxWorks或Mentor Graphics Nucleus等小型实时操作系统(RTOS),非常适合于CPE设计。增强型DSP指令集可直接在CPU内核上运行,满足一些DSP需求,不需要另外一个独立的DSP处理器。

EDN嵌入式微 处理器基准协会(EEMBC,www.eembc.org)提供了一套完整的嵌入式处理器测试标准。EEMBC Netmark?网络基准是一套路由测试标准。其包含开路最短路径第一(OSPF/Dijkstra)算法,数据包流路由基准,路由表算法等。该基准对处理器在网络运用时实现的功能进行了模拟。

这套测试基准中包含压缩的路由测试基准,用实际的IP帧结构执行数据打包和路由表查询。该基准可使用不止一个长度的路由表,因而更为高效。这避免了合成测试基准中单一尺寸路由表的缺陷。ARM为ARM946E-S内核提供Netmark基准。在与ARM签订了NDA之后,您可获得该基准。

PrimeXsys双核平台

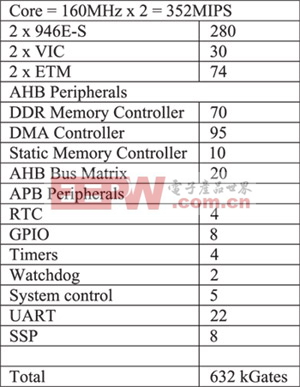

PrimeXsys双核平台(图3)提供了可扩展、预集成的基础级IP,支持RTOS的直接运行。946 DCP采用多层AMBA?片上总线体系结构,在交叉型AHB总线矩阵中支持多重总线管理,并提供非常高的带宽。在946DCP中添加IP,可以用主、从方式访问系统总线。相应地,AMBA外设总线(APB)为速度较慢的外设提供了更节能的片上系统连接方式。

每个内核内都含有向量中断控制器(VIC)和嵌入式跟踪宏单元(ETM?)。当内核全速工作时,ETM监控ARM指令和数据总线,在与跟踪调试工具进行数据交换前,将数据暂存到MultiTrace?分析器中。

表1为946 DCP中IP主要模块的性能指标。

表1. 双核平台模块门数(单位:千门)

评论