基于FPGA的高速异步FIFO的设计与实现

本文引用地址:http://www.eepw.com.cn/article/149633.htm

3 仿真验证

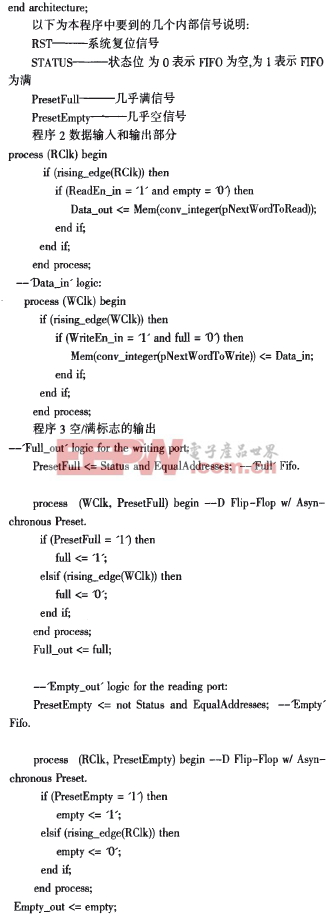

基于以上的分析结合实际本文构造了一个8192x8的FIFO,用MODELSIM进行仿真。对该异步FIFO编写测试向量进行仿真,如图2所示。

图2仿真波形图

图2中,WClk为写时钟,Writeen_in为写使能,Full_out为满信号,Data_in为数据入,RClk为读时钟,ReadEn_in为读时能,Empty_out为空信号,Data_out为数据出,Clear_in为系统清零信号。上面部分为写地址产生模块部分的信号波形,从图2中可以看出.在写时钟的上升沿.在写时能为高有效期间擞据开始输入到RAM里面,而在读时钟的上升沿,在读时能有效时,在本仿真时间的195ns处.开始输出数据。将程序下载到LATTICE公司的FPGA芯片中,经过测试验证,系统的时钟频率可达33MHz。

4 总结

本文主要研究了用FPGA芯片实现异步FIFO的一种方法。详细阐述了空,满标志信号的产生方法。按照以上思想所设计的异步FIFO已经在实际电路中得到了应用。实践证明他可以解决大多数异步FIFO电路常见的错误。同时增加了系统的可靠性和应用灵活性。

本文作者创新点:通过对FPGA芯片内部EBRSRAM的深入研究.提出了一种利用格雷码对地址进行编码的异步FIFO设计方案。实践证明.增加了系统可靠性和应用灵活性。

评论