嵌入式系统应用中NV SRAM存储器的应用

传统方案中常常采用EPROM、EEPROM和Flash存储程序,NVSRAM具有高速存取时间和与SRAM相同的接口,因而可用于存储程序。本文介绍NVSRAM如何与基于程序和数据存储的微处理器进行接口,并说明选用NVSRAM与现有的其它非易失存储器相比具有哪些优势。

本文引用地址:http://www.eepw.com.cn/article/149199.htm尽管EPROM、EEPROM、Flash和NVSRAM在某种程度上提供了相同特性的非易失存储方案,而在一些特殊应用中,不适当的存储器方案将会导致设计缺陷。微处理器系统选择存储器时主要面临下列问题:

1。对特定的应用,存储容量不足;

2。程序存储器需要较快的存取时间;

3。保证非易失存储的写周期次数不够大,产品工作在有效寿命的后期时存在可靠性问题;

4。扇区写入不可避免,特别是存储器的扇区大于微处理器的缓冲区时。

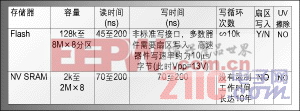

5。采用UV擦除方式不便于开发,一般无法满足在线编程的要求,需要特殊的附加设备,而不适当的操作会导致数据在光照下被擦除。表1列出了四种存储器的不同特点,显然,NVSRAM的综合指标最高。

EPROM的缺陷在于需要UV擦除时间,编程时需要额外的高电压Vpp和Vcc。EPROM为程序存储提供了一种可行方案,在微处理器应用中能够提供适当的接口和读时间,但由于缺少电擦除功能无法用于非易失数据存储。

EEPROM是一种较好的程序存储方案,但其有限的写周期次数和较低的写速度使其很少用于数据存储。写周期次数的限制使其在大多数应用中只能用于程序存储。

初看起来,Flash是一种很好的解决方案,它同时提供了同步和异步读功能,与EPROM和EEPROM相比具有较高的写速度。但Flash存在写周期次数有限的问题,划分后的扇区(64字节到64k字节)必须一次性写入。这意味着数据必须由微处理器高速缓冲,然后一次写入Flash器件的存储区内。如果设计中微处理器不具备足够的内部RAM,就无法缓存这些数据。在一些应用中,如数据记录仪,当电源出现故障时可能导致滞留在微处理器缓冲区的数据丢失。尽管市场上也有一些Flash器件不需要扇区写入,但产品的订货批量受限制。另外,这种产品还缺乏Flash器件标准,虽然大多数Flash器件的异步读操作与SRAM或EPROM相同,但并非所有器件都是如此,而且,写接口标准较多,当产品更新换代无法支持相应的标准时将限制器件的实际使用寿命。另外,还需保证写操作不要超出最大写周期次数,因为当器件达到有效寿命时将开始出现随机存储误码。有些Flash存储器需要提供额外的编程电压(大于13V)以保证快速写模式,因而增加了系统成本,而寻找容量低于1Mb的Flash也比较困难。

NVSRAM可提供16kb至16Mb的存储容量,存取时间高达70ns。读、写接口均与SRAM保持一致,标准Vcc条件下NVSRAM与同等速度SRAM的操作完全相同。无需担心存储数据分区问题,数据存储位置与标准SRAM相同。电源失效时(Vcc跌落到标准工作电压以下),内部电路将片选(CE)信号置位,使存储器处于写保护状态、并切换电源以便保持数据。电源恢复正常后,NVSRAM恢复微处理器对CE信号的控制,SRAM电源切换到Vcc。CE信号被切换的瞬间只要微处理器控制信号没有处于写有效状态(CE为高)就不会丢失数据。

由于工作状态下NVSRAM与SRAM兼容,可以用速度相符的NVSRAM简单地替代任何微处理器系统的SRAM,这种替代仅有的制约是需要了解电源所能提供的电流。Dallas半导体建议采用CPU监控电路以保证微处理器在NVSRAM就绪之前处于复位状态。微处理器复位状态下,绝大多数总线控制信号(CE、WE、RD)处于禁止状态,能够避免NVSRAM在有效期内数据不丢失。Maxim提供多种CPU监控电路,完全胜任这项工作,配合其它与复位信号相关的功能就能保证系统更加可靠工作。

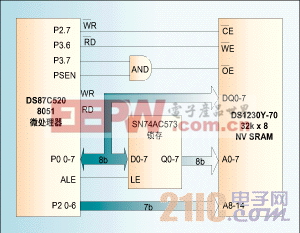

图1是利用单片NV

SRAM存储程序和数据的典型电路,该电路的主要优点是节省了元器件数,充分利用了存储器空间。如果微控制器仅占用32kB存储空间的1kB存储程序,则其余31kB可用于非易失数据存储。32kB的存储容量足以满足许多应用场合,如果对程序和数据分别采用两类存储器将造成不必要的浪费,而且将迫使设计人员选用更大容量的存储器。

利用NVSRAM存储数据

NVSRAM非常适合在微控制器系统中存储校准信息、记录数据等。如上所述,与SRAM工作在相同速度的NVSRAM采用标准的Vcc电源,NVSRAM在读、写操作时不需要延长时钟周期,除非与高速DSP或先进的微控制器配合使用。

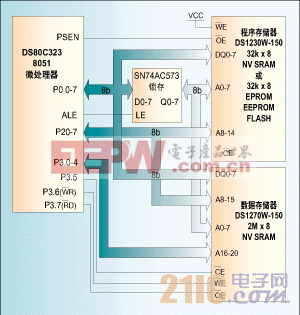

绝大多数微控制器、包括8051系列产品,均提供程序存储器和外部RAM的控制信号,图1表明了如何利用这些现有的控制信号产生一组新的单片NVSRAM控制信号,同时用于程序和数据存储。图2表示3V系统中如何利用现存的控制信号对两片独立的存储器寻址,主要区别是PSEN用于程序存储器输出使能控制,8051的RD信号(P3。7)用于数据存储器的输出使能控制。当两个存储器输出同时驱动到总线时,会导致总线冲突;另一种出现总线冲突的可能是微控制器将数据输送给NVSRAM的时候,外部存储器受指令控制输出数据。这些情况都需要在设计中慎重考虑,以避免总线冲突。

针对这种设计需要说明两点:首先,程序存储器必须始终加写保护;其次,数据存储器的可寻址空间可能大于微处理器寻址空间。

当NVSRAM的WE引脚置为高电平时,不能写入任何数据,因此,需利用存储器编程器对该引脚进行编程。BPMicrosystems和DataI/O编程器几乎支持所有Dallas半导体的NV

SRAM。当采用编程器进行器件编程时,注意在把器件安装到电路之前要避免器件受ESD冲击,因为ESD冲击会造成器件中的数据丢失。一旦器件在保证数据正确的前提下装入线路板,NVSRAM将有效保证数据的完整性。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论