基于DSP和CPLD的金属磁记忆检测仪设计

1.2 DSP与CPLD及相关外设通信

随着DSP芯片的工作时钟越来越高,指令的执行周期越来越短,而挂接在系统上的外设,如:按键、显示屏、蜂鸣器等,速度各不相同,且均相对DSP来说,速度较慢,DSP如果直接对这些片外模块进行控制,将会带来很大的时间开销。在本系统中,DSP对外设的控制经常需要用到种类较多的门电路、译码电路、时序电路等,为了节约PCB板的面积,增加系统设计的灵活性、可靠性,采用CPLD实现DSP的外围电路控制,能充分地利用CPLD中的资源,减少软件编程的复杂度,提高DSP的执行速度。这样,DSP对每一个外设都分配一个地址,CPLD通过DSP传过来的地址线、控制线和数据线来进行对相应外设的控制。对于按键类型的外设,当按键按下后,首先CPLD对按键进行消抖,CPLD得到按键值后,再通过中断通知DSP,DSP再通过总线来读取按键值。

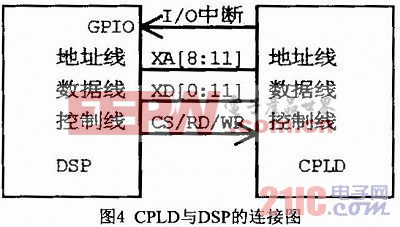

TMS320F28335通过四位地址总线(XA[11:8])、数据总线(XD[11:0])、外部读写使能信号(RD、WR)、片选信号(CS)及I/O中断信号与CPLD相连,由这些信号连线完成DSP对CPLD内的相关寄存器或I/O的读写操作。挂接在CPLD上的所有外设DSP都可以通过地址线XA[8:11]来分配一个对应的地址,当在DSP中执行写指令:*(0x0400)=0x001时,地址总线XA[11:8]=0100B,数据线XD[11:0]=0x001,同时控制线中CS、WR为低电平,RD为高电平,CPLD接收到总线电平后,进行地址锁存、数据译码等操作,即可对相应地址上分配的外设进行控制。CPLD与DSP的连接关系如图4所示。本文引用地址:http://www.eepw.com.cn/article/149112.htm

1.3 TFT真彩液晶屏

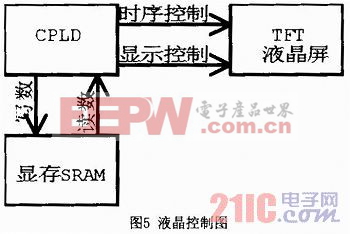

液晶屏分辨率为272×480,尺寸为4.3英寸。显示色彩为16位,RGB各占6位、5位、6位,采用3.3V电压供电。CPLD上外挂一片16×256 kB的SRAM作为显示屏的显存,存储一帧屏显的数据。CPLD将DSP总线上传来的数据,先存入显存,然后再从显存中读取出来,配合液晶屏驱动时序,在液晶屏上将波形显示出来。图5为液晶控制图。

评论