采用上位机与FPGA开发板的光纤通道接口适配器设计

2.3 Virtex-5开发板的底层保证

(1)系统构造逻辑设计主要完成以下几点功能:

本文引用地址:http://www.eepw.com.cn/article/148771.htm控制PCIE硬核实现与上层软件交互;对上层传输数据加CRC校验;完成FC链路初始化过程;完成FC流控功能;完成FC-2差错处理;控制ROCKET I/O把上层软件数据通过ROCKET I/O发送;控制ROCKET、I/O把接收恢复的数据传输到上层软件。

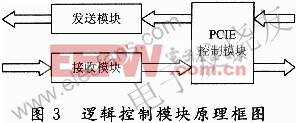

(2)逻辑设计的模块组成:底层逻辑控制模块主要完成FC物理层通信,它主要包括发送模块、接收模块和PCIE控制模块三部分,每个模块又根据功能不同划分多个子模块,在PCIE控制模块中,有一些缓存来存放接收模块传送过的数据和相应的数据信息,发送模块也会从PCIE控制模块的缓存中读取数据传送出去,其原理框图如图3所示。

数据发送模块 该模块通过读取上位机的状态信息来发送不同的信息,当ACK使能时,该模块发ACK,当数据使能时,该模块就发送固定帧数的数据,发送的数据是从缓存中读取,CRC由该模块添加。空闲时就发送IDLE码。

数据接收模块 接收模块包括接收控制模块、CRC模块和临时缓存模块。主要完成数据和链路控制帧以及准备信号的接收,并实现CRC校验,根据帧头来判断不同类型的数据帧或控制帧,并存入缓存中,同时将帧的相关信息也放入相应的缓存中。

PCIE接口控制模块 该模块主要根据PCIE总线上的地址对应的寄存器的值,译码成相应的使能把PCIE总线上数据写入相应的数据发送buf-f,ACK发送 buff反之根据逻辑输入的使能,译码成对应的PCIE总线上对应地址的对应寄存器的值,并把数据接收的buffACK接收buff数据写入相应的PCIE地址上。

2.4 最终实现

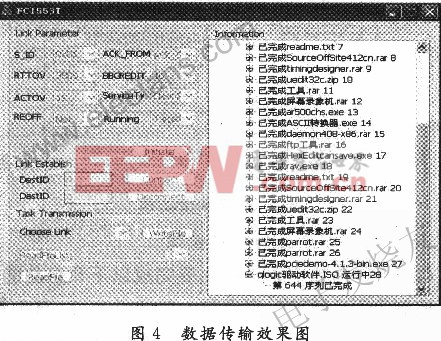

通过上位机与FPGA开发板的结合,实现了光纤通道接口适配器的高速性。传输效果图如图4所示。

3 结语

通过上位机与FPGA开发板的结合,模拟并实现了光纤通道在高速数据传输过程中接口处的设计。尽管该设计是上位机配合FPGA的形式实现,但仅就设计思路而言,对于实际开发光纤通道接口适配器具有一定的借鉴意义。

评论