基于CPLD和MAX7000系列的数据采集系统简介

5 CPLD构成的ISA总线接口

在PC系列机中,I/O空间是独立的,共有1KB(地址编号为000H~3FFH)。由于I/O接口一部分分布在主机母板上,另一部分分布在扩展槽上,所以I/O的1024个口地址也分成两个部分,其中前512个由母板上的接口控制器使用,后512个供扩展槽内的接口控制卡使用。而且由于后512个地址中的一部分已经被配置成系统资源的接口,所以真正能被用户设计开发的I/O端口为数不多,而且不连续。这样就不能采用常规的用PC机提供的地址总线来寻址双口RAM的方法,因为这种方法只能寻址其中为数不多而且不连续的一些单元。所以这是一个难点。为此,采用用PC机的数据线来寻址双口RAM的方式,只需占用三个I/O端口,就能寻址整个4K的RAM区。

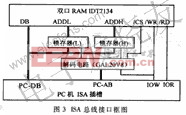

ISA总线接口电路逻辑框图如图3所示。

本文引用地址:http://www.eepw.com.cn/article/148518.htm

采用了ISA插槽中的8位数据线、10位地址线、读写控制线IOW和IOR以及电源线,并假设使用390H、391H、392H三个端口。当PC机要访问某一地址单元时,首先通过390H端口将低8位地址送到数据总线上。此时由PC-AB送出的390H信号和IOW信号经解码电路输出一个锁存脉冲到锁存器(L),将此低8位地址锁存;然后通过391H端口将高4位地址送到数据总线上,此时由PC-AB送出的391H信号和IOW信号经解码电路输出一个锁存脉冲到锁存器(H),将此高4位地址锁存;最后通过392H端口进行读写,只要PC-AB上出现392H信号,解码电路就输出一个低电平到双口RAM的/CS,再根据相应的读写控制信号就能进行读写操作。

用ALTERA公司的EPM7064SLC84-5实现这一接口的VHDL文件如下:

仿真结果表明此电路设计完全可以实现上述功能。PC机使用端口392H读取双口RAM中的数据时的仿真图如图4所示。

CPLD是现代电子工程领域的一门新技术,它提供了基于计算机和信息技术的电路系统设计方法,提高了设计电路的集成度和可靠性。笔者在将ALTERA公司推出的MAX7000系列产品应用于高速数据采集方面做了尝试,具体使用EPM7032和EPM7064设计了地址发生器、数据总线控制器和ISA总线的接口,目前已经将其应用在电力系统某精确故障定位系统中。

评论