基于DSP的有源降噪系统分析与研究

本文引用地址:http://www.eepw.com.cn/article/148302.htm

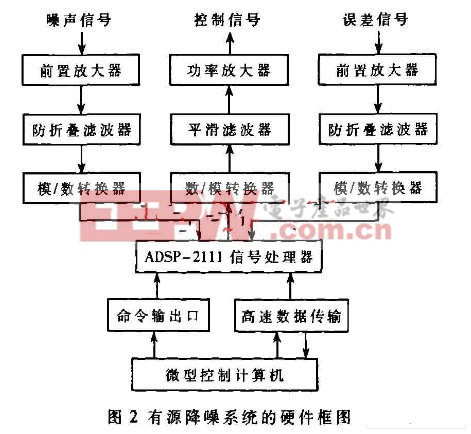

为实现此系统,其硬件设计框图如图2所示。

图1中的传声器MIC1、MIC2拾取的噪声信号和误差信号,经过三极管放大后,进行防折叠滤波处理以及模-数转换,将数字信号直接送入DSP和主机中,对实验数据进行分析,将得到的控制信号进行数-模转换,经平滑滤波、放大后驱动图1中的扬声器S,使控制信号和噪声信号相叠加,完成有源降噪的过程。

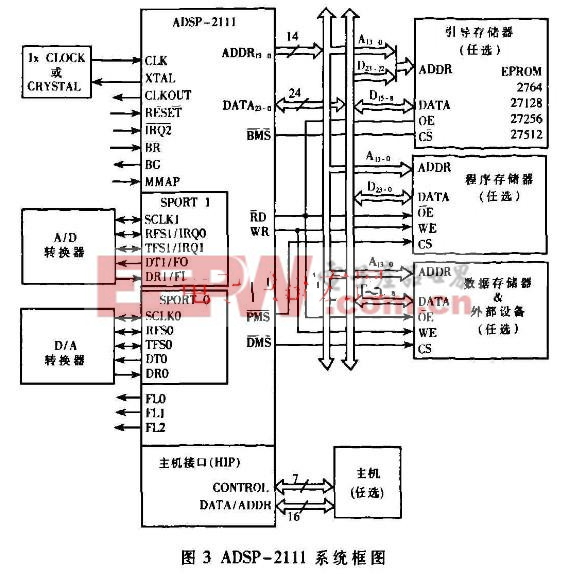

2.1 ADSP-2111信号处理器

系统中数字信号处理器选用AD公司的16位定点的ADSP-2111芯片,其核心结构如图3所示,特点如下:

(1)ADSP-2111芯片采用哈佛结构,片内有6条总线(1条程序总线、2条数据总线、2条地址总线和1条DMA总线),这种分离的程序总线和数据总线,可允许同时获取指令字(来自程序存储器)和操作数(来自数据存储器),而互不干扰。这样可以在1个周期内同时准备好指令和数据,对于数字信号处理中的许多运算,要比一般的单片机速度快得多,这对于实时性要求非常高的噪声控制来说,是非常必要的。

(2)ADSP-2111采用流水线操作,以减少指令的执行时间。执行一条指令要通过取指令、译码、取操作数和执行几个阶段,流水线操作使4条不同的指令处于激活状态,这极大地提高了运算速度,体现了DSP的优越性能。同时,其内部含有硬件乘法/累加器,从硬件上实现了乘法器和累加器的并行工作,可在单指令周期内完成1次乘法并将运行乘积求和的运算。

(3)ADSP-2111是带有主机接口HIP(Host Interface Port)的芯片,能较方便地与PC机接口。HIP为并行I/O口,允许ADSP-2111做主机存储器映像的外设,其操作速度与ADSP-2111的总线速度相似,主机对DSP程序的加载及与DSP之间的数据通信均通过HIP接口来完成。

评论