基于双DSP硬件架构的固态开关控制系统设计

在该控制系统中,主DSP实现切换控制功能。系统故障以开关信号形式通过外部中断送入主DSP,以保证系统的高速响应。主DSP输出的晶闸管控制信号通过FPGA输出至晶闸管触发模块。协DSP负责主、备用侧电源质量的监控,其主要功能为电压跌落检测。监测结果以“开关信号”以及“16位数据”两种形式输出。本文引用地址:http://www.eepw.com.cn/article/148106.htm

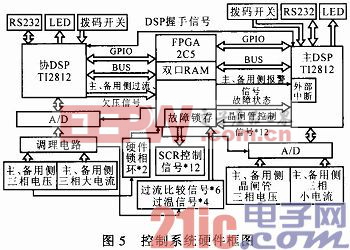

如图5所示,主、协DSP除单线GPIO直连端口外,主要通过FPGA相连。连接端口包括并行系统总线端口和通用I/O(GPIO)端口,分别用于传递“16位数据”和“开关信号”参量。并行系统总线端口用于连接DSP和FPGA内置的双口RAM。该数据端口可使主、协DSP以兆赫兹级的速度并行通讯,适合传输大量的系统参数。GPIO端口则用于快速传递各种故障状态。此外,FPGA还负责实现底层保护功能,微处理器如DSP虽可满足系统智能化控制需求,但一些不可预知事件会导致控制系统出现严重故障。因此,除DSP外,系统利用FPGA增加了纳秒级控制速度的底层保护功能。如图5所示,系统电流与温度开关信号经过模拟信号调理模块形成过流、过温故障信号后,直接送入FPGA。当系统发生过流、过温故障时,FPGA故障锁存模块将使晶闸管控制信号失效。整个保护过程所涉及信号处理单元少,结构简单,大大提高了系统的可靠性和响应速度。在此将进一步介绍各主要控制系统功能模块的实现方法,并给出实体装置的运行结果。

4 主要系统功能的实现

4.1 主DSP功能

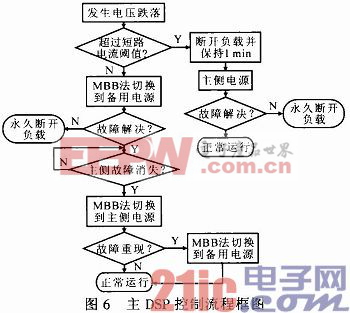

改进后的切换控制流程如图6所示。

由于系统采用双DSP控制架构,每个DSP运算量较小,采用TMS320F12812型DSP芯片即可满足需求。根据SSTS控制系统需求,主DSP主要配

置了外部中断、外部存储器接口、SCI等外设。其中,外部存储器接口用于连接FPGA内置的双口RAM。根据系统仿真结果,主DSP程序在MBB控制基础上增加了对故障位置的判断。当故障发生在负载侧即故障电流很大时,应切断负载一段时间后(大于系统继电保护重合闸时间),再次尝试接入电源。若重新投切仍不成功,则说明负载故障无法恢复,不再切入任何电源。

4.2 同步信号采样的实现与改进

在电力系统运行中,由于种种原因可能引起电网频率漂移,若采样周期不是实际周期信号整数倍,会造成频谱泄露,从而引起误差。采用锁相环跟踪锁定电网频率可解决该问题。硬件锁相环电路主要由方波产生信号电路和锁相倍频电路两部分组成。由过零比较电路产生的50 Hz方波信号经过锁相倍频电路产生12.8 kHz采样频率信号。该电路结构简单,响应速度快,但在系统发生缺相故障或谐波干扰时,硬件锁相电路将可能无法可靠跟踪电网50 Hz信号,造成采样电路工作不正常。该控制系统将硬件锁相环输出信号送入FPGA进行频率检测跟踪,当跟踪输出的电网频率与50 Hz偏差大于1 Hz时,由FPGA输出标准12.8 kHz采样触发信号,以保证系统可靠运行。

评论