基于Flash和JTAG的FPGA系统

3.1 设计的FPGA实现

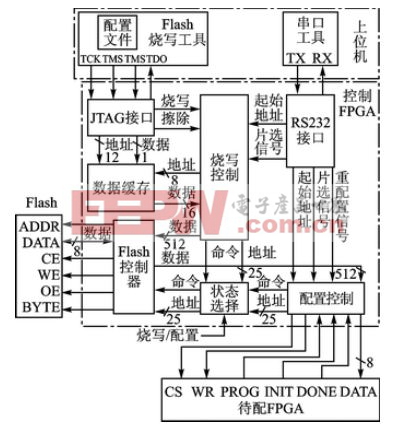

控制FPGA实现的逻辑控制功能包括与上位机软件iMPACT和串口工具通信、烧写Flash以及配置FPGA器件。基于模块化的设计思想将具体功能分解成多个模块,如图3所示,数据与地址通道上的下标为其通道宽度。各模块作用如下:

1,RS232接口模块接收来自串口工具的配置文件地址及重配置信号,配置文件地址译码后得到对Flash存储器进行各种操作时的起始地址,重配置信号则用来触发FPGA配置文件的切换。

2,JTAG模块包括JTAG接口模块、数据缓存模块及烧写控制模块。JTAG接口接收JTAG下载线上的JTAG指令和数据后,若为FERASE或FPGM指令则向烧写控制模块发送擦除或烧写信号,若为FDATA0指令则接收TDI上的串行数据并存入数据缓存模块中。数据缓存模块利用片内BRAM来实现,可存放一帧配置码流。烧写控制模块接收到擦除信号后,产生擦除命令和操作地址并发往状态选择模块;接收到烧写信号后,从数据缓存模块读取配置码流,产生的写命令、操作地址发往状态选择模块,操作数据则直接发往Flash控制器。

3,FPGA配置模块接收到来自RS232接口模块的起始地址和重配置信号后,先向待配FPGA器件发送初始化信号,等待初始化完成后向状态选择模块连续发送读命令和操作地址,并利用从Flash控制器返回的配置码流来配置FPGA器件。

4,状态选择模块根据外部的烧写/配置信号选择Flash控制器的输入,从而决定控制FPGA目前处于烧写Flash存储器状态还是配置FPGA器件状态。若为“0”,则输入烧写控制模块产生的命令和地址,控制FPGA处于烧写Flash存储器状态;若为“1”,则输入配置控制模块产生的命令和地址,控制FPGA处于配置FPGA器件状态。

Flash控制器响应这些输入的命令、操作地址和数据,产生与命令相对应的Flash存储器控制时序,并返回Flash存储器的数据输出。

3.2 性能实际测试

本方案处于编程模式时,系统能够通过JTAG接口和串口与上位机软件进行正常的通信,在加载合适的配置文件后,可以完成Flash存储器的擦除和烧写操作,实测烧写速度为160 Kb.需要烧写多个配置文件时,通过串口工具发送配置文件地址,即可对不同的Flash空间进行操作。

处于配置模式时,以Virtex系列中XCV1000型FPGA为配置对象,其配置文件大小约为5.84 Mb,实测一次配置时间为60 ms,计算得知配置速度约为97 Mb/s,远大于System ACE解决方案的30 Mb/s.如需切换不同的配置文件,从串口工具发送配置文件地址及重配置信号,即可实现多个配置文件的实时切换。

结语

本文分析了各种传输协议接口以及System ACE多配置解决方案的优缺点,根据实际应用需求,提出了一种基于大容量NOR Flash并利用JTAG接口完成配置码流下载的FPGA多配置系统解决方案。本系统采用Flash存储器替代配置用PROM或CF卡,节省了硬件成本和空间,且理论上可以支持不限数量的配置文件切换,对FPGA的配置速度也达到了System ACE方案的3倍以上。

fpga相关文章:fpga是什么

存储器相关文章:存储器原理

评论