一种基于ARM和FPGA的环形缓冲区接口设计

2.2 发送程序设计

首先介绍数据的发送过程,也就是数据帧从ARM到FPGA的发送流程。程序分为两个部分,一个是ARM端的程序,负责将来自用户的数据组成最大不超过256双字节的数据帧,然后向FPGA内部的发送缓冲区写数据帧;另外一个是FPGA端的程序,负责将接收的ARM数据帧写入发送缓冲区,同时将各个子缓冲空间的数据依次提取出来,传递给物理层进行发送。

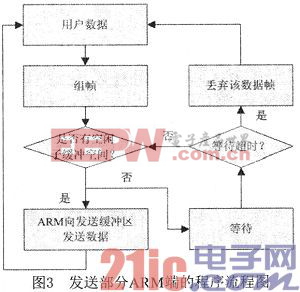

发送部分ARM端的程序流程图如图3所示。将用户数据首先组装成规定大小的数据帧,然后判断发送缓冲区是否有空闲的子缓冲空间,若发送缓冲区满则等待,否则将数据帧发送到统一编址的发送缓冲区空间。本文引用地址:http://www.eepw.com.cn/article/148003.htm

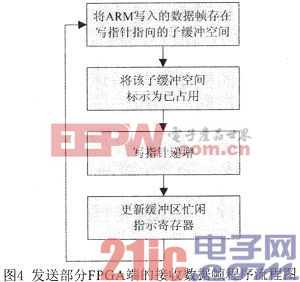

发送部分FPGA端的程序流程可分为接收ARM写入的数据帧和将发送缓冲区中的数据帧发送给物理层进行数据处理。这两部分的程序流程分别如图4和图5所示,主要是利用子缓冲空间的忙闲状态与读写指针的变化来控制数据帧的读取和写入,实现子缓冲空间循环利用以及数据帧的正常发送和缓存。

fpga相关文章:fpga是什么

评论