USB 3.0 电路保护

现如今市场上有几种不同的防静电抑制技术,例如MLVs(多层陶瓷压敏电阻),聚合物ESD抑制器和半导体的ESD抑制技术。是否选择了正确的保护将决定USB3.0端口是否可以承受ESD事故。

本文引用地址:http://www.eepw.com.cn/article/145483.htm设计师们必须特别关注器件电容,钳位电压和动态电阻,因为这些参数对选择最佳ESD保护至关重要。一些设备保护制造商设计出了有着最小寄生电容以提高信号的最大完整性的产品,同时有些产品的钳位性能达到了最大化虽然代价是电容很高。

像TVS二极管和二极管阵列的半导体有着最低动态电阻,提供卓越的钳位性能,并能保持非常低寄生封装电容。图5示出了硅的钳位性能与MLV ESD保护技术的对比。正如可以看到的,以硅为基础的解决方案的钳位电压更低。

USB 3.0的眼图测试结果如图9中所示,美国力特的TVS二极管阵列,通过结合低钳位电压和低电容ESD保护给USB 3.0应用程序提供了最好的保护技术。

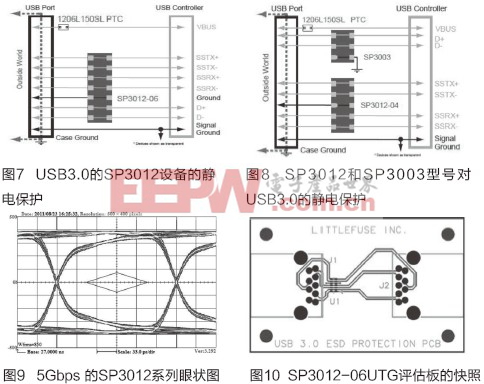

TVS二极管阵列比如美国力特的SP3012-06UTG型号等设备提供多通道ESD保护解决方案,USB 3.0保护的最佳选择。美国力特的SPA® 设备的工作方式有两种。首先,它们的二极管能吸收瞬态电流,泻放电流;第二,能通过雪崩或齐纳二极管来钳制电压电平。图7显示的是美国力特USB 3.0设备SP3012-06UTG型号的静电保护解决方案。

它提供6行±12kV静电保护,能够确保保护单一3.5x1.35mm的包装里的所有USB 3.0数据线。美国力特SP3012-06UTG免除了设计人员为使用多个ESD保护装置而占用宝贵的电路板空间的担心。此外,SP3012具有仅为0.4Ω的极低动态电阻,这为USB 3.0芯片组提供了同类产品中一流的钳位性能和对过压事件非常敏感的收发器芯片。

另外,如果设计人员希望实现两个设备解决方案,推SP3012-04UTG和SP3003-02UTG,它们可用于保护那六行数据线(参见图8)。SP3003保护传统的D + / D-对,而SP3012则可以保护两个极速差分对。

信号完整性

保持USB 3.0数据完整性是至关重要的,任何少量的附加电容都可以导致信号失真,并降低信号的可靠性。测试静电抑制器的寄生电容对信号完整性的影响的方法之一是进行眼图测试。此测试需要对重复的数字信号进行采样,并在示波器上显示所得到的眼孔图样。眼图经常被用来定义可接受的信号质量和依从性。

图9显示了美国力特SP3012-06UTG用一个5Gbps的USB 3.0符合性测试图案和掩模“通过”的眼状图。图10显示了该评估板的PCB布局。为了模拟一个真实的世界USB 3.0数据路径,测试电路板是用90Ω差分信号对和USB3.0接口设计的。

由图可以看出,信号一直在掩模边界内,而且眼图宽度是保持不变的,这样给设计者在系统电容预算内提供了很大的灵活性。

电路相关文章:电路分析基础

评论