从头到尾构建混合信号高集成度系统(SOC)的步骤(5):电路仿真

Dave:大概如此。我知道我们需要一个输出放大器,所以我们获得了这方面的一些帮助。输出放大器的规格易于制定,但在CMOS中是一个需要技巧来构建的模块。在此之后,我们开始依次增加均衡器级,在每次添加后利用电缆模型进行仿真。我们使均衡功能有效,但还要记录失真、功率预算和DIE面积预算。

本文引用地址:http://www.eepw.com.cn/article/141904.htmTamara博士:看似有许多要考虑的事情。

Dave:是,但魔鬼就在细节里。一位老员工有次对我说,(对此种开发来说)“偏执狂才是正确的心理状态。”

Tamara博士:伍迪艾伦有次说,“偏执狂知道所有事实。”

Dave:说得太对了!

Tamara博士:好了,现在我们有了所有模拟处理级,接下来如何测试整个系统呢?

Dave:在学校里,你只是运行功能仿真测试。而在业内,我们是设计具有制造可行性的电路。制造工艺具有容差。掺杂程序具有范围,晶体管因之能够运行得稍快或稍慢一些。我们需要仿真最佳和最差条件,来获得我们器件的最佳产率。

Tamara博士:我想你还需要考虑温度。这些组合的图表看上去可能像这个:

Dave:良好的开端!现在你需要解释无源元件——如电阻和电容——的容差。你能看到情形的数量会如何激增而使你永远不能完成设计!

Tamara博士:你还需要做一些事情来减少你需要运行的仿真的数量。或者至少限制参数值对制造容差的依赖性。

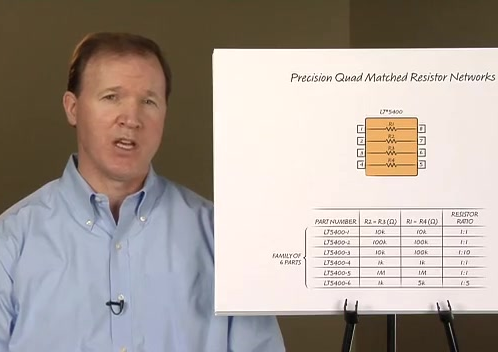

Dave:就这样了。有许多设计技巧可供使用。一种是使用电阻器的比率值而非精确值。两个电阻器值可以一起增大或减小,所以比率在某种程度是不变的。尽管在所有情况中我们都会使用少量动态余量(过度设计)来确保我们能够满足我们的目标要求。

Tamara博士:你的过度设计量达到多少?10%?

Dave:我希望我们进行10%的过度设计。不过通常我们没有这样大的余地。我们的2毫米×2毫米原始尺寸目标和功耗技术规格将会限制我们的实现能力。

Tamara博士:你还从未谈到静电放电(ESD)。我知道这可能是一个挑战。

Dave:实际上我们有ESD方面的专家来帮助我们将合适的电路用在正确的引脚上。这里也有重要的权衡考虑。ESD二极管具有很大的容性且随电压而变化,所以在我们应用ESD时我需要重新运行失真仿真。

Tamara博士:测试呢?你在设计中如何帮助进行器件测试?

Dave:对于数字器件,我们有一种称为‘扫描’的测试,它包括一些特别的测试,例如把所有的触发器串联起来。运行扫描测试可保证所有电路链中的所有触发器的有效性。还有一个叫做“覆盖率”的参数,它让我们知道我们实际上测试了数字器件的多大部分。该参数最好能达到90%以上。

Tamara博士:模拟测试呢?

Dave:在设计过程中,我们制定了一个测试计划,该计划描述了将在生产中如何对每个模块进行测试。通常,该测试会揭示缺陷且常常导致进入特别测试模式。

Tamara博士:哪种测试模式?

Dave:嗯,这里有一个易于理解的例子:我们需要知道我们的内置振荡器的运行频率,所以我们设计一个简单的基于外部标准的时序脉冲的频率计数器。基本上,然后我们用一个寄存器来支持该功能,并从另一个寄存器读回结果。这种模式非常快而干净,并可节省测试时间。

Tamara博士:还有其他模式吗?

Dave:有些东西是不能说的,有权利保护。(他说的时候眨了个眼)我饿了。

Tamara博士:很好。来杯啤酒和一大块那种鲑鱼怎么样?

Dave:好,听你的!

评论