Altera全新Qsys工具加速FPGA产品上市步伐

在FPGA设计领域目前存在着三大主要难题:设计规模扩大、设计重用、设计验证时间太长。这三大难题严重影响着FPGA设计的效能,将减缓产品由研发到上市的时间,是亟需解决的重点问题。

本文引用地址:http://www.eepw.com.cn/article/130918.htm2012年3月30日,“Altera亚太区采用Qsys实现系统集成研讨会•北京站”在清华大学举行,该活动重点介绍了Altera新的系统集成工具Qsys,及其如何通过Qsys提高设计效能。

简化设计过程

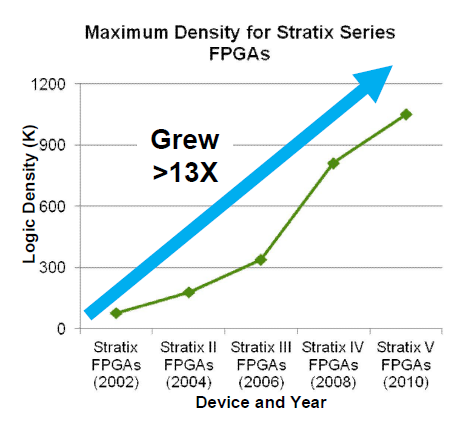

随着半导体技术的不断发展,由于半导体工艺的不断提升,器件的集成度也随之提升,FPGA器件的逻辑密度也急剧增加,因此使得设计开发的规模不断扩大,复杂度上升。目前,FPGA 器件密度已经提高到百万逻辑单元(LE),因此,设计团队需要实现更大更复杂的系统,在更短的时间内满足越来越高的性能需求,传统的设计模式显然已经跟不上硬件的发展速度。

图1 Altera Stratix系列FPGA逻辑密度增长

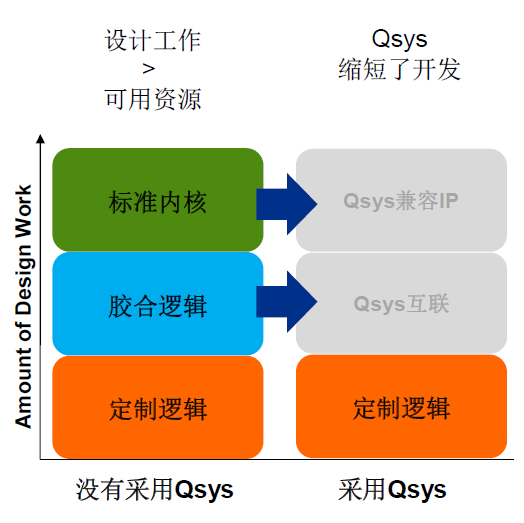

FPGA设计工作主要包含三个部分:标准内核、胶合逻辑和定制逻辑。标准内核部分一般采用相应的标准IP进行设计,胶合逻辑部分主要是实现FPGA内部各部分(标准内核、存储器、定制逻辑等)间的互联,定制逻辑则是设计者自主开发实现差异化的部分。Qsys采用的是系统级开发,通过片上网络架构,可以大幅简化设计工作,提高设计效能。Qsys包含多种兼容IP,如PCIe、DDR3、JTAG、UART等,可以把标准内核部分的工作降至最低。Qsys能够自动完成部分诸如接口协议、存储器等相关的繁琐且容易出错的集成任务,极大地提高了设计效率。这样,Qsys使得设计者可以把大部分的精力都放在定制逻辑部分。

图2

提升设计重用

当前半导体行业内人才流动是很大的,现任工程师和将来的工程师想要重复使用前任工程师曾经开发的设计,难度是很大的。在设计重用的过程中常常会出现以下问题:工程师需要对接口进行重新设计;工程师需要为各种修改后的设计提供支持;缺少相应的文档,使得其它工程师无法得知接口是如何工作的。

图3 Altera公司亚太区产品市场经理谢晓东

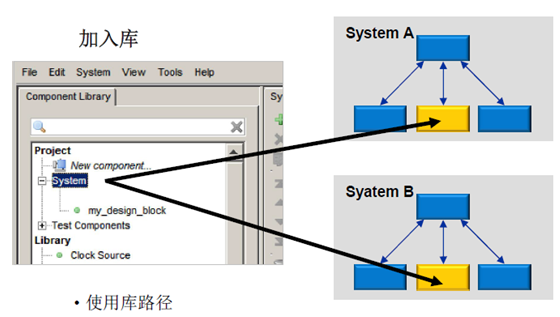

据Altera公司亚太区产品市场经理谢晓东先生介绍,Qsys是业内首个提供子系统设计重用的FPGA开发工具。Qsys增强了设计重用功能,提供标准接口如Avalon、AXI3、AXI4等,使得设计者不需要重新设计接口。Qsys提供了组件编辑器来让用户增强RTL设计,同时,Qsys还可以自动封装和改进用户的设计,让用户可以将自己的设计打包为独立IP,并且首次做到将子系统打包,极大地方便了日后设计重用和共享。

图4 Qsys打包设计便于重复使用

加速设计验证

在设计完成之后,通常需要花费大量的时间对设计进行验证以确保设计的正确性,这一过程常常超过了设计本身所花费的时间。特别是随着设计规模的不断扩大,验证的复杂度和难度也迅速膨胀。

通过提取/探测100/1000寄存器的方式进行验证将花费大量的时间,而Qsys采用了通过读写操作的方式进行验证,如图所示,通过对地址位置进行读写操作,先确定出现问题的模块,再针对出现问题的模块进行更细化的验证。以这种方式可减少证流程,缩短验证设计所需的时间,加快产品上市的步伐。

图5 Qsys同过读写操作进行设计的验证

评论