基于Spartan-6的多路网络数据采集卡设计与实现

引言

本文引用地址:http://www.eepw.com.cn/article/127893.htm随着互联网的迅猛发展,网络监控的需求日益迫切。为了实现对网络实时监控,有必要及时全面地收集、分析网络的数据,准确获取网络信息,对网络的信息进行监控,及时发现可能会出现的问题。然而随着网络带宽的增加和规模的扩大,大规模网络数据采集面临着数据规模庞大和数据到达速度过快的挑战。为了克服上述困难,通常采用硬件实现完成数据采集功能。

随着FPGA的发展,其内部资料日益丰富,速度和性能大大提高,特别是内部嵌入了大量IP核,使得FPGA上进行高速网络数据采集成为可能。本文涉及的多路网络采集卡系统采用Xilinx的Spartan 6系列中XC6SLX45T FPGA,获取8路10/100M RJ45端口送来的网络数据包,并将数据包发送到PC机进行分析和监控,最终根据分析结果来判断网络中的异常情况。

系统概述

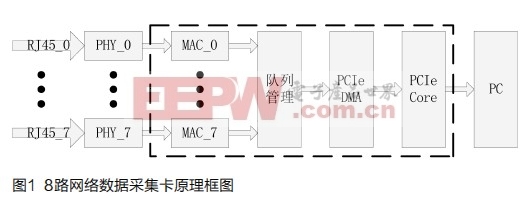

系统框图

图1所示为系统的原理框图。8路10/100M网络数据通过RJ45接口送入到PHY芯片,PHY芯片完成转换之后,通过MII接口送到FPGA。FPGA中集成了8路MAC核,将网络数据输出到队列管理;队列管理对每路MAC的数据包进行管理,并输出到PCIe的DMA模块;DMA模块将数据包发送到PCIe硬核,直接写入到PC机的内存,以便PC机进行分析。

队列管理

由于网络数据的包大小不同,在一个包没有读完之前有可能第二个包到来,因此有必要对网络的数据包进行队列管理,避免数据包丢失的情况。

本系统中的队列管理采用双口RAM和FIFO联合构成,其中双口RAM用来存储数据包,FIFO用来存储数据包的起始地址和结束地址。当FIFO有数据时说明RAM中有数据包,如果此时并没有数据包在向DMA中写数据,那么就可以读出当前数据包写入到DMA模块;如果此时正在向DMA模块写数据,则等待写完后再读下一个包。

由于网络数据和PCIe DMA模块的时钟处于两个时钟域,所以采用双口RAM和FIFO也可以起到数据同步的作用。

评论