2.5D堆叠硅片互联

摩尔定律认为芯片上的晶体管数量每过18个月就会翻一番,过去20年,不管是和FPGA厂商还是ASIC厂商都在遵循在这个定律的发展,随着微电子技术更深入地改变人们的生活,摩尔定律似乎成了芯片技术发展的约束-----如何更早地实现裸眼3D电视?如何更快地提升无线通信带宽?如何实现低功耗高速存储?没有更强大的芯片推出,这些愿景从提出到实现需要漫长的时间,现在,赛灵思公司提出的2.5D堆叠硅片互联SSI)技术有望破除摩尔定律的魔咒,并有望彻底改变IC产业的游戏规则!

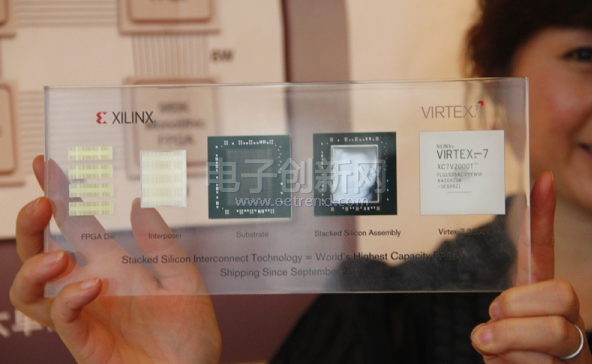

本文引用地址:http://www.eepw.com.cn/article/127250.htm今天,赛灵思公司全球同步宣布推出首批28nm Vitex7-2000T FPGA,这是利用2.5D堆叠硅片互联打造的全球容量最大的FPGA,它有195万个逻辑门,68亿个晶体管,单从晶体管数量上来说它也是世界最大的半导体芯片!它的运算能力是1.5TMACs ,其容量是同类产品的两倍,这个技术让FPGA的发展超越了摩尔定律,“这是一个可以game change的技术!”赛灵思全球高级副总裁亚太区执行总裁汤立人评价道。

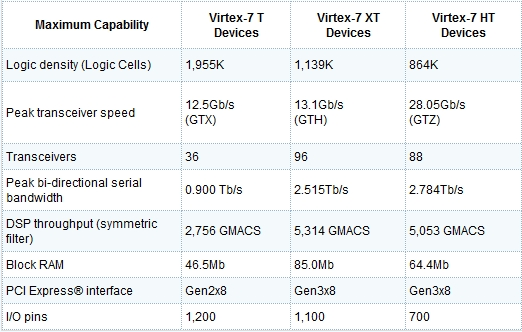

“你可以把它想象成一个巨大的处理平面,它可以处理海量的信息,它有2000个DSP,单个FPGA实现180,000MIPS指令,它就像一个超级计算机!而它的功耗只有19W!”赛灵思公司产品市场营销总监Brent Przybus强调。“未来我们还会推出针对某些特定应用的版本,例如我们已经推出了Virtex-7 XT和Virtex-7 HT,它们分别增加了高速收发器的数量,峰值带宽超过2.5Tbps!”

这一强大的FPGA让许多需要2年后完成的酷炫产品提前面市了!“例如目前大家看好的全视角裸眼3D电视技术,这种全视角裸眼3D需要电视分析观看者的视角,然后对内容针对视角进行处理,现在还没有强大的ASIC可以处理这些海量信息,但是Vitex7-2000T的推出,让实现不在遥远。”汤立人指出,“预计明年初就将有真正全视角3D裸眼电视推出了。”

他举例称,有某无线厂商3年前规划产品时,提出的需求是需要2000万门的ASIC,性能要达到Tb级别、功耗预算为30瓦,开发时间为2年,但是,现在3年过去了,该产品的开发现状是采用多芯片方案,不但需要ASIC,更需要两块Virtex-5完成处理,而且功耗高达70瓦!这还没有计算因项目延长造成的资金投入和市场损失,“如果采用Vitex7-2000T FPGA,同样可以完成规划目标,但是功耗要低于30瓦、而开发时间仅为ASIC的1/3!上市时间等于缩短了2年!这给厂商带来的好处大家都可以想象到!” 汤立人强调,“所以Vitex7-2000T FPGA推出后广受客户欢迎,目前我们有2000个design in !而且已经有基于Vitex7-2000T的产品出货了!”

赛灵思Vitex7产品特性一览

2.5D芯片堆叠与3D芯片堆叠的纠结

3D芯片堆叠的概念已经提出了很多年,但是如何实现3D芯片一直是产业在探讨的难题,目前,真正实现3D芯片的只有mems芯片,“我们认为从目前的芯片到真正的3D芯片还需要数年的时间,而2.5D芯片堆叠是个不错发展方向,会延续很久。”汤立人指出。“而赛灵思能完成2.5D芯片堆叠,也是得益于其独特7系列独特的架构,这种架构可以支持FPGA进行方便的伸缩,如果没有这种独特的架构,很难采用这种堆叠互联技术。”

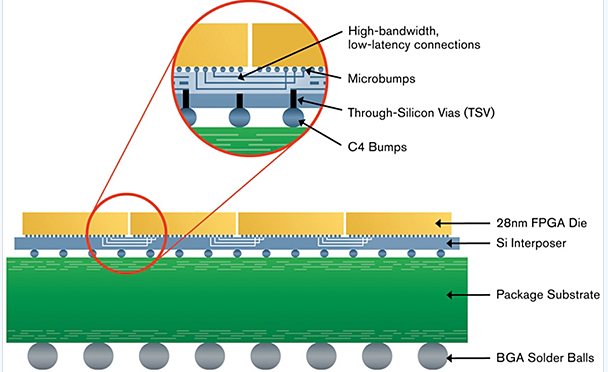

所谓2.5D是指在无源器件上堆叠有源芯片,而3D芯片是指在有源芯片上堆叠有源芯片,赛灵思打造的2.5D堆叠技术是在无源硅中介层上并排几个硅切片(有源切片),该切片再由穿过中阶层的金属连接,中介层在每个芯片间提供10000多个高速互联,这与PCB上不同IC通过金属导线互联通信类似,这个架构的特点是,Vitex7-2000T虽然有4个切片组成,但设计人员功过赛灵思的设计工具可以将其看作一款大型FPGA进行操作和开发。

堆叠硅片互联技术封装示意图

很多人担心由此引发的热管理问题,对此,汤立人解释说由于中阶层是无源的,所以除了FPGA芯片本身有功耗外没有其他热问题,它其实就是一个单芯片器件,不用特殊的降温设计。而由于其内部采用AMBA以及AXI4高速互联总线,内部互联产生的功耗远小于四个器件外部互联方式产生的热量,所以采用2.5D堆叠技术的FPGA所产生的功耗要远低于四个单独器件的功耗。

另外,采用SSI封装架构的内应力小于同样大小的单片式倒装片BGA封装,因为中介层能有效分解堆积的内压力,所以这种封装还提升了芯片的热机械性能。

汤立人透露赛灵思早在2006年就开始堆叠芯片互联技术的研发,以后不断在90nm、65nm、28nm工艺上进行集成和模块化开发,终于今天正式推出28nm 堆叠工艺技术的FPGA,这真可谓5年磨一剑,而这个技术也为整个半导体产业带来福音,“2.5D芯片堆叠互联技术也可以用于其他IC产品,我们认为这个技术会不断演进下去,直到数年后3D堆叠技术成熟后它还会有自己的生命力。”汤立人表示,“2.5D堆叠技术未来会从目前的同构系统向异构系统发展,这意味着利用堆叠技术可以把不同类型的器件集成进去。在我们的堆叠中,FPGA采用的是28nm工艺,而无源中介采用的是65nm工艺,这意味着什么?显然,未来,采用2.5D堆叠技术工艺,可以给高工艺的FPGA集成更多其它工艺器件,比如65nm的模拟器件,40nm的memory等等。”

SEMICO更预测FPGA未来会集成标准单元、分立器件、多核处理器、光学器件等等,到那时,FPGA会变成什么? 发挥你的想象力吧!

赛灵思全球高级副总裁亚太区执行总裁汤立人(中)、赛灵思亚太区上销售与市场总监张宇清(左)与赛灵思公司产品市场营销总监Brent Przybus(右)

赛灵思亚太区上销售与市场总监张宇清指出:“Vitex7-2000T FPGA的推出给ASIC原型开发带来提升,原来64个FPGA完成13个ASIC模拟验证,而且只能进行10套软件系统的开发,而现在只要16个Vitex7-2000T FPGA就可以完成13个大型ASIC模拟验证,并进行200套系统软件开发,这在ASIC设计效率的提升是非常惊人!”这其中有趣的现象是ASIC的设计效率提升得益于FPGA的发展,而FPGA又在不断取代高端ASIC,“因为随着工艺的演进,高端ASIC的风险和成本惊人,例如28nm的NRE费用就达4000万美元,这还不算芯片修改的费用,而用28nm FPGA, NRE费用是零!”张宇清举例道,“另外,ASIC和FPGA各有其发展市场,也不能对立的看待,不能用简单的取代来看两个产品。”

前天,台积电宣布28nm工艺正式量产,共有5家厂商量产,其中FPGA厂家就有两家,随着工艺技术的高速发展,一个以FPGA为引领者的时代到来了!

评论