评Xilinx的28nm从三重氧化物到HIGH-K

本文用老百姓看得懂的语言介绍前两天XILINX 28nm FPGA所采用TSMC的HIGH-K金属栅工艺(HKMG)新闻的重大意义。

本文引用地址:http://www.eepw.com.cn/article/127049.htm跑冒滴漏的晶体管

近10年来,当集成电路进入亚微米阶段,当人们享受到摩尔定律带来的好处时, 一朵乌云,一直笼罩在集成电路业界的上空,就是越来越严重的跑冒滴漏现象。 作为集成电路的最基本组成单元,晶体管,当尺寸越来越小的时候,漏电缺越来越严重,不仅传统漏电的地方漏,本来不该漏电的地方也开始从涓涓细流满满发展成波涛汹涌。 就像上图的那个漏水的水龙头。

刚开始,漏水的地方主要是出水口和进水口直接的部分, 因为水流主要在这里流动。 慢慢地,水龙头越来做越小,人们发现,主要的漏水的地方从原来的进水口和出水口出,移到了中间用来拧紧水龙头的部分。哪怕你不经常开关水龙头,可这个地方会持续不断地渗水。 如果拆开水龙头来看,出毛病的地方通常是一个橡胶作的皮垫。水龙头尺寸做小了以后,皮垫的尺寸跟着缩小,以至于太薄,水直接从皮垫渗出。 就像这张图:

多垫皮垫解决漏水问题

皮垫太薄导致漏水解决办法是什么?简单,多垫几层皮垫,一层不够两层,两层不够三层。 这样,中间漏水的问题就可以暂时解决了。

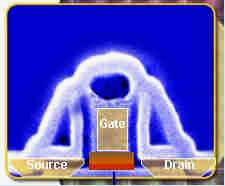

用来进行栅极绝缘的绝缘层,一般是用二氧化硅做的,相当于水龙头中的皮垫, 通常只需要一层。 但是,赛灵思的Virtex-2, 用了两层氧化物。从90nm开始赛灵思的Virtex-4,65nm Virtex-5,40nm Virtex-6,都采用了三重氧化物栅极的工艺,降低漏电流,从而达到降低静态功耗的目的, 三重氧化物栅极长得是这个样子滴:

当然,皮垫垫多了,跑冒滴漏解决了一些,可是开关起来肯定不够灵活,因此,这种工艺只是在非关键区域使用,比如用于配置FPGA的地方。 真正需要高速的区域,还是采用一层氧化物工艺。 因此 Virtex-2, 4,5, 6 尽管在降低功耗上做得很出色,可和精心设计的ASIC比,仍然有差距。 毕竟那么多闲置的资源在那里,每个跑冒滴漏一点,数千万个加到一起,就不是小数字。

赛灵思的竞争对手没有用三重氧化物这个方法,而是用统一抬高衬底电压的方法,降低栅和衬底的电压。此方法投机取巧,就像水龙头漏水了,就把总闸关小一点,这样,漏水虽然看上去小了,可是你想用水的时候,流出水的速度也大大降低。体现在性能上,就是所有的管子速度降低。

评论