JEDEC准备迎接DDR4内存规格

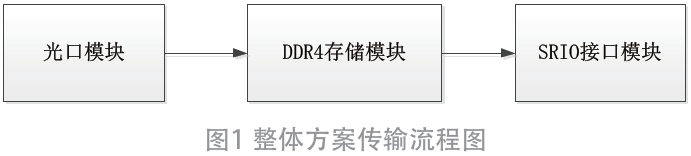

内存芯片的双倍数据速率(DDR4)的标准将包括三个数据宽度的产品,差分信号传输,数据屏蔽和一个新的终止计划,根据JEDEC的固态技术协会,标准开发商制定的标准。

本文引用地址:http://www.eepw.com.cn/article/122847.htmDDR4标准预计将在2012年中期出版,和上一代技术相比,在减少电力消耗的性能上提供了显着进步,JEDEC(弗吉尼亚州阿灵顿)于周一(8月22日)说。 DDR4标准出版时,将公布在JEDEC的网站上,该组织说。

DDR4正在开发一系列功能的设计,使高速运转,并在各种不同领域,包括服务器,笔记本电脑,台式电脑和消费电子产品的广泛适用性,JEDEC说。它的速度,电压,和架构都被定义目标为简化迁移和促进通过标准,据该机构说。

JEDEC说一个DDR4电压的路线图已经提出,将有助于客户迁移VDDQ的恒定为1.2V,允许在未来的电源电压VDD减少。DDR4通过保持的I/O电压稳定,将有助于防止技术过时,JEDEC说。

每个引脚的数据传输速率,随着时间的推移,将从初始的1.6千兆每秒向每秒3.2千兆传输的最大目标转移,JEDEC说。与DDR3超过其预期的1.6 GT/s的峰值相比,在未来DDR4提出的很有可能是更高的性能水平,JEDEC说。

DDR4标准列入计划的其他性能特点是伪开漏输出接口的DQ总线,齿轮减速模式为2667 Mhz的数据传输速率,世行集团的架构,内部产生的VrefDQ,和改进培训模式,JEDEC说。

DDR4标准的其他亮点包括:

- 新的JEDEC POD12接口标准为(1.2V)DDR4。

- 三个数据宽度的产品:X4,x8和x16。

- 差分信号时钟选通。

- 新的中止计划相对先前的DDR版本:在DDR4上,DQ总线转移终止到VDDQ,这样即使VDD电压是随着时间的推移降低也能保持稳定。

- 名义和动态的ODT:改进ODT的协议和一个寄存模式考虑到可以让标称终端和动态写入终止,而无需驱动的ODT引脚。

- 脉冲时间8和突发长度4。

- 数据屏蔽。

- DBI:帮助降低功耗,提高了数据信号的完整性,此功能通知是否真实或倒置的数据应存储的DRAM。

- 新的CRC数据总线:启用错误检测数据传输能力 - 尤其是有利于写操作期间,在非ECC内存应用。

- 新的CA校验命令/地址总线:核实链接的命令和地址传输的完整性,所有的操作提供一个低成本的方法。

- 支持DLL关闭模式。

JEDEC表示,它计划举办一个关于DDR4新标准的技术研讨会。宣布与出版更多的信息和细节将一致。

“大量的内存设备,系统,组件和模块生产商正在合作来完成的DDR4标准,这将使下一代系统完成更大的性能与较低的功耗”JEDEC的JC-42.3DRAM存储器小组委员会主席,Joe Macri在一份声明中说。

评论