FAE讲堂:提升创造力的数字设计工具 FPGA Editor

Block视图的按钮条包含许多其它选项。值得一提的是 F= button 按钮,其功能是显示逻辑片中使用的项目的完整配置。例如,如果使用了一个LUT6和一个触发器,按下 F= 按钮将会给出LUT的布尔议程以及触发器的配置模式。

本文引用地址:http://www.eepw.com.cn/article/119298.htm阅读赛灵思用户指南是一回事,而从计算机屏幕上展开的视图上探察所有逻辑、开关和参数则是另一回事。一旦熟悉了FPGA构造及所有资源,那么在编写和验证设计时获得的帮助将会令人感到惊奇。

在设计流程中记录生成补丁脚本

当用户在GUI环境中编辑设计时,FPGA Editor能够记录用户动作。用户不仅可以保存记录动作流程,还可在以后重新使用记录的脚本并加以重复。当无法更改RTL,但又需要在设计过程中对设计进行修改时,这一功能特别有用。

假设设计采用了第三方 IP 或赛灵思加密IP,其中包括一个全局时钟和一个DCM来生成称为interface_clk的时钟。然后

再假设接口所连接的ASIC出现问题,无法在预定的interface_clk的上升沿接收数据。如何修正这一问题?

当然,你可以改变PCB,更换出现问题的ASIC或者让第三方IP小组来修改时钟输出逻辑以提供90度相移的interface_clk。所有这些解决方案都既耗费时间又成本高昂。一个更简单的建议是利用FPGA Editor来记录修改动作,

对interface_clk逻辑进行必要的更改,从而为出现问题的ASIC提供正确的时钟相位。一旦有了相关修改的FPGA Editor脚本,就可以回放这些命令行脚本记录的修改步骤,而你也可以正常继续你的FPGA设计流程。当出现问题的ASIC修复正常以后,你只需要将FPGA Editor 脚本从编译脚本中移除就可以,而interface_clk也会恢复其正常的行为。

要想对设计进行手动编辑,首先需要在FPGA Editor中开启读/写(read/write)权限。在菜单条中点击 File →Main Properties在此菜单下,可以调整编辑模式(从No logic Change到Read/Write)。点击Apply,现在就可以开始对设计进行编辑了。在下一步利用FPGA Editor记录对设计进行的所有修改时,只需要简单地从菜单条中点击Tools → Scripts →Begin Recording。FPGA Editor将会提示输入一个脚本名字(如patch.scr)。输完脚本名字,就可以对设计进行必要的修改了。

在设计中运行设计规则检查(DRC)来看一下是否有规则冲突的红色标志是一个很好的方式。在我的设计例子中,有14条警告,但都可以忽略。下一步我们将需要定位 interface_clk 使用的DCM,并为此DCM的90度相移输出创建另一个称为DCM_clk90_out的时钟。这需要利用全局时钟布线资源将时钟连接到BUFG。要增加一个BUFG,先在FPGA构造中找到一个未用的BUFG位置,右击并选择Add(添加)。然后,工具会提醒你为 BUFG 命名(clk90_bufg)并确定其类型:BUFG(参见图1)。

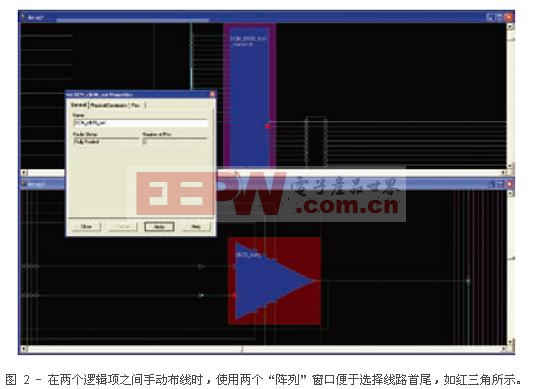

创建了新的BUFG,就需要将其输入和输出连接到适当的位置。在本例中,DCM的9 0度相移输出将驱动BUFG。在窗口Array1中,点击DCM的90度输出端衰减器,在窗口Array2中,点击BUFG的输入端衰减器,同时按住Ctrl键,可实现连接。然后释放Ctrl键,点击鼠标右键并选择Add。工具会提示为新网络连接输入名字。这样就将DCM和BUFG通过新网络连接到一起了(参看图2)。

clk90_bufg 的输出要代替由原interface_clk驱动的IOB上的时钟。要将IOB从原来的时钟域中移开,需要定位IOB,标注时钟输入端衰减器并按下Delete键移除这一连接。这样我们就可以将新的clk90_bufg时钟连接到这儿,从而完成整个补丁。要连接BUFG(clk90_bufg)的输出,按住Ctrl键不放,在窗口Array2中标注BUFG的输出端衰减器并在Array1窗口中选择IOB的时钟输入。松开Ctrl键,点击鼠标右键显示选项菜单并选择Add。这样就最终完成了BUFG输出和IOB之间的连接,而IOB则用来驱动下游ASIC的新建接口,利用interface_clk90时钟就可以正确地捕获传输的数据。

评论