在赛灵思FPGA设计中保留可重复结果

高扇出信号

本文引用地址:http://www.eepw.com.cn/article/119148.htm高扇出信号通常会成为设计中的决定因素。即使大部分综合工具支持扇出控制,在 HDL 中复用这些信号来得到可重复性更高的结果也是明智之举。设计人员应该把这种策略和指令结合起来,以确保综合工具不会移除这些重复信号。如果一个高扇出信号位于逻辑顶层,则可以复用该信号,然后用单独信号驱动每一个顶层模块。

如果综合工具扇出控制不能得到预期结果并且无法修改 HDL,那么在BRAM 的 MAP 逻辑中采用寄存器复用约束条件以及最高扇出约束条件,往往会产生比综合更好的寄存器复用选择。更多相关信息,请参阅 《约束条件指南》(UG625) 中的 MAX_FANOUT。做为一个常见的调试问题,跨越层级时保持一致的信号名称更便于追踪存在问题的路径。如果信号名称经常改变,则很难追踪时序报告和其它调试输出。把信号方向放入所有模块或实体的端口定义中也有所裨益。

综合优化

综合会对可重复结果产生巨大影响。如果从综合过程得不到最佳输出网表,就无法在实施工具中产生理想条件。设计人员可以采用多种综合技术帮助改善实施结果。

在执行综合时采用时序约束条件至关重要。用户往往会在综合过程中过度约束,然后在赛灵思实施工具中放宽时序约束条件。这样可以增加综合工具负担, 从而减轻实施工具的负担。

接下来使用综合工具产生的时序报告。如果一条路径在综合与实施过程中无法满足时序要求,则可以修改 HDL或综合选项,以便在综合之后满足时序要求。这样可以在实施阶段节约时间。

在综合过程中得到可重复结果是在实施工具中得到可重复结果的最佳途径。大多数综合工具支持自下而上的流程,其为设计的顶层以及各个下层模块建立了独立综合项目。用户可以根据HDL 变更情况控制更新网表。大多数商用综合工具都具有增量流程。

平面布局规划的重要性

平面布局规划把组件定位到设计中的一个具体位置或者范围。这可以减少布局变化,从而提高设计的可重复性。通过平面布局规划或者采用位置约束 (或兼而用之)通常可以实现更高的性能。

也就是说,糟糕的平面布局规划或位置约束会导致无法达到时序要求。平面布局规划有一定技术含量,要求具备工具和设计方面的高级知识。你可以采用符合时序要求的实施结果做为指导原则来创建理想的布局。

如果主板需求是选择引脚布局的

主要因素,FPGA 实施工具可能很难获得时序维持可重复结果。但是设计人员可以借助多种有助于实现可重复性的技巧。

首先要清楚数据流。比如,数据会从中心 I/O 流向侧 I/O。可以把与总线相关的所有引脚保持在 FPGA 的同一领域,以此限制控制信号的布线距离。I/O总线控制信号布置在相关地址与数据总线附近。需要一起优化的信号应当布置在一起。如果更关注主板布线,则在 I/O上利用流水线技术优化寄存器有助于改进引脚布局差强人意的 FPGA 布线。

区域组平面布局规划

区域组平面布局规划是一种高级平面布局规划技术,其定义了模块在FPGA 之内的位置。虽然该技术易于使用, 但常常被误用, 从而导致所解决的问题比所造成问题更多这一糟糕平面布局结果。有一些出色平面布局规划的总体指导原则可以帮助您避免走入上述误区。应当使所有区域组保持相似的利用率。比如,应避免让一个分组利用率达到 60% 而让另一个达到 99%。不要重叠区域组。唯一的例外情况是,如果两个不同的区域组具有需要布置在一起的某些逻辑单元 , 则允许重叠 CLB 的一、两行或列。此时用户负责确保为两个区域组约束提供足够资源。

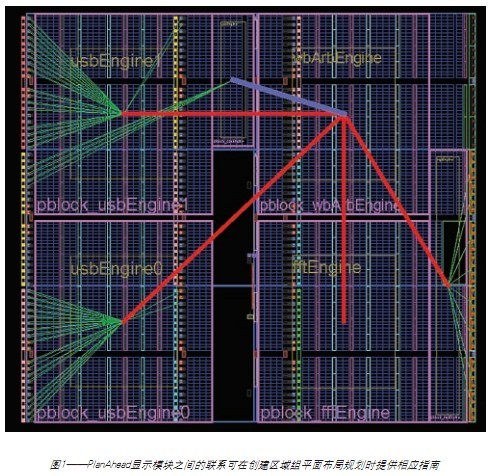

如果需要把设计的两个不同逻辑部分放在相同物理位置,则应当把它们放入同一个区域组。一般允许一层嵌套,也就是父区域组中的一个子区域组。如果一个大区域组里的一小部分需要布置到某个狭窄区域, 则需要上述分层。仅对设计中的关键部分进行平面布局规划而让相关工具决定非关键逻辑的布局非常重要。连接到固定资源 (如 I/O、收发器或处理器块)的逻辑可能会从平面布局规划中受益。可以采用顺利实施的结果做为准则来确定布局或时序问题。诸如赛灵思 PlanAhead ™软件 (图 1)和时序分析器等工具有助于可视化显示相关问题。

尽可能减少各个全局时钟所用区域数量以及各个区域的时钟 (区域与全局)数量一般会有所裨益。如果您准备为某个时钟域的增加更多逻辑,切勿过度约束,而应当进行相应规划。如果某个时钟域的时钟全部投入使用,则很难找到有效布局。而 PlanAhead 软件所提供的对齐时钟域功能可以简化上述平面布局规划工作。对于拥有 10 多个时钟域的Virtex® FPGA 设计而言,当前实施方案所用的时钟域位于 .map 报告文件中, 同时还附带了 UCF 约束条件。

评论