全景图像实时展开在FPGA上的实现

由于ADV7180产生的视频数据流是隔行扫描数据,分为奇数场和偶数场,所以SDRAM控制器除了对数据流进行存储,还要在读取数据时进行去交织操作。SDRAM控制器的双读口设计可以出色地完成去交织任务。在读取数据时,利用VGA的行扫描信号控制这两个读口分别读取:当VGA控制器扫描到奇数行时,由第一个读口读取相应奇数行数据;否则,由第二个读口读取相应偶数行数据。之后,再合并这两个读口读取的数据得到逐行扫描的、分辨率为640×480的视频数据流。

本文引用地址:http://www.eepw.com.cn/article/117270.htmYCbCr到RGB转换模块

本系统的最终目的是将视频流输出到VGA显示器进行显示,而从SDRAM读取得到的数据是YCbCr422格式,不符合VGA显示要求,所以需要将其转换为RGB数据格式。

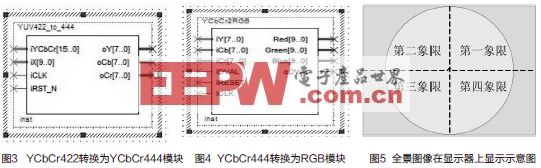

首先将YCbCr422格式转换为YCbCr444格式。在每一个时钟上跳沿,判断当前VGA列扫描信号,若当前列为奇数,则将SDRAM读口得到的16位YCbCr信号的前8位赋值给Y作为当前像素的Y值,后8位赋值给Cr作为当前像素的Cr值,Cb保持不变;若当前列为偶数,则YCbCr的前8位仍为当前像素的Y值,后8位为当前像素的Cb值,Cr保持不变。这样就保证了输出的Y、Cb、Cr三个信号是当前像素的对应描述信号。

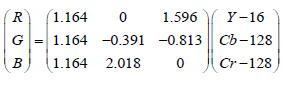

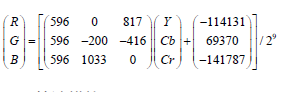

在确定了每个像素对应的YCbCr值之后,就可以通过如下公式计算得到对应的RGB值。

DE2-70上的EP2C70 FPGA芯片内嵌了150个乘法器块,每一个乘法器块可以配置为两个9×9位的乘法器或者一个18×18位的乘法器。所以本系统使用QuartusⅡ中集成的MegaWizard Plug-In Manager配置乘加器模块用于实现YCbCr颜色空间到RGB颜色空间的转换。另外,上述转换公式涉及浮点运算,在Verilog中不易实现,所以将公式中各浮点值左移9位变为整数,从而公式调整为:

−展开算法模块

−展开算法模块

展开算法模块为本系统的核心模块,利用EP2C70内嵌的M4K存储器和正余弦生成器实现了极坐标视图到直接坐标视图的实时展开。

人眼视角约为120°。考虑到人眼观察的习惯,系统将圆形的极坐标视图分割成为第一、二、三、四象限四个部分,每部分90°,由使用者选取感兴趣的部分进行展开,这样既符合人眼观察的习惯,又节省了空间。

视频分块

全景极坐标视图在显示器上显示时类似于图5,其中矩形代表整个显示器显示的内容,分辨率为640×480,圆形代表全景图像出现的位置,半径大约为240个像素,所以可以按图5中虚线部分将视频每一帧分为4块,每一块分辨率为240×240。系统使用VGA控制器生成的行列扫描信号标定当前像素的位置,当像素位置位于全景图像区域内时,则将像素值存入M4K存储器,否则继续搜索下一个满足条件的像素。

M4K存储器设计

M4K存储器是内嵌在EP2C70中的存储器块,其中每一块容量达到4096bit,可配置为真双口存储器,在EP2C70芯片上共有250块M4K存储器块。本系统使用了209块M4K存储器块,借助其高寻址精度,实现图像的实时展开。

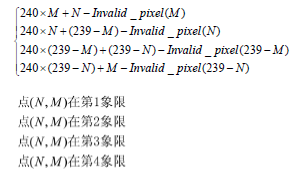

M4K存储器写地址

将数据写入M4K存储器时,可以将数据流按照图像显示顺序全部存入,这样就需要生成0~360°的所有正余弦查找表;同时,由于存入了全部图像信息,将会有1/4左右的无效像素点,浪费了宝贵的存储器资源。系统利用M4K存储器精确的寻址操作将第二、三、四象限的信息在存入时进行翻转,使得存入M4K存储器的图像仅显示为第一象限的特性,则只需要生成0~90°的正余弦表就可以完成对整幅图像的展开计算。其次,固定摄像头之后,圆形全景图像在显示器中的位置是固定的,所以可以确定每一行有效像素的坐标范围。当行列扫描信号在此范围之内,则将该像素值存入M4K存储器中,否则,继续寻找下一个符合条件的像素点。所以,对第i象限的第M行第N个像素,如果为有效像素,则存入M4K存储器的地址按如下规则计算:

这里的M和N取值范围均为[0,239],Invalid_pixel(K)表示在第K行第一个有效像素之前所有无效像素点总数。

fpga相关文章:fpga是什么

色差仪相关文章:色差仪原理

评论