基于暂态行波法的配电网故障定位装置研究

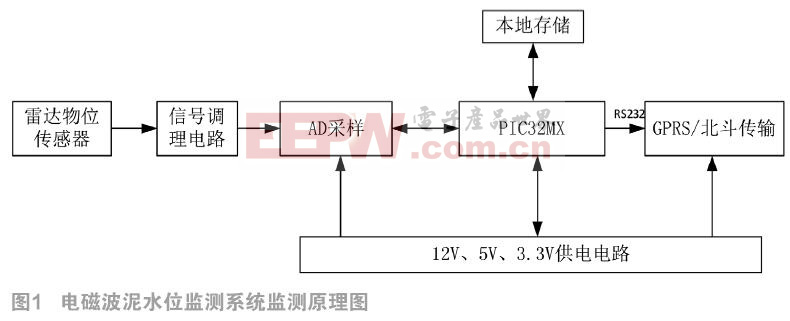

信号调理电路

本文引用地址:http://www.eepw.com.cn/article/115728.htm由于电压传感器输出的电压信号不正好在ADC的量程范围内,故需要对信号进行调理,以满足高速ADC的要求,保证ADC的正常工作,避免造成ADC的损坏。

高速数据采集及存储电路

高速数据采集及存储电路是行波法故障定位装置的核心部分,主要由FPGA、ADC模数转换器和2片SRAM构成。其中,FPGA采用Altera公司的240引脚PQFP封装的EP1C12,它具有12, 060 LEs、52个M4K RAM blocks、2个PLLs、173个用户I/O。ADC采用ADI公司的AD7822,它是一种8-bit A/D转换器,单极性输入,并行输出;内含取样保持电路,具有转换后自动Power-Down的模式,电流消耗可降低至5μA以下。转换时间最大为420ns,可满足1μs采样一次的转换要求,SNR可达48dB,INL及DNL都在±0.75 LSB以內。可应用在数据采样、DSP系统及移动通信等场合。SRAM的任务是存储高速ADC转换的数据,由于高速ADC的转换速率很高,这就要求数据存储器有较大的存储容量和较短的读/写时间,这里采用ISSI 公司的IS61LV25616。IS61LV25616是256k×16的高速异步CMOS静态RAM,读写速度可达10ns,完全可以满足要求。

具体工作过程: 线路正常运行时,没有暂态信号输入,3片AD7822在FPGA产生的高频时钟脉冲控制下并行地进行采样和数据转换,并将转换的数据循环存储在2片SRAM中的一片上,SRAM中永远保留着等于RAM容量的最新数据。当三相故障行波信号中任一相的幅值高于预设的门槛值时,表明有故障行波信号被监测到,锁存当前的时标,同时开始一个10ms的计时延时,在这段时间内继续将ADC转换的数据存储到当前的一片SRAM。当10ms延时结束时,切换地址数据总线将采集的数据存储到另一片SRAM上,同时通知MCU取走第一片SRAM中的故障行波数据和锁存的时标,并通过GPRS DTU远传给中心端服务器做进一步的处理,实现故障波形分析,进而实现故障定位。若只采用1片SRAM,在10ms延时结束后,需暂时停止数据采集,待SRAM中数据取走之后才能重新采集数据,以保证有用的故障信息不被冲掉。如果在转存暂态数据期间线路发生故障,则不能对其进行监测,造成故障数据漏记,无法定位。采用双SRAM,由于MCU转移数据和高速ADC继续采集数据可以在FPGA的协调下同时进行,从而在一定程度上解决了以往装置存在的循环存储器死区问题。

单片机外围电路

单片机(MCU)外围电路主要包括3部分:与GPRS DTU连接的数据远传电路、与GPS模块连接的时间获取电路和与FPGA之间的数据通信电路。根据单片机需完成的功能,本系统中采用Microchip高性能RISC CPU PIC18F8520,它内部有32kB的FLASH程序存储器和2kB的SRAM数据存储器、1kB的EEPROM数据存储器;运算速度可达10MIPS;可以工作在DC~40MHz的时钟频率范围之内;具有外部存储器接口,可方便地访问外部存储器中的程序或数据,便于与FPGA的数据通信;具有2个USART接口,支持RS-485和RS-232,其中一个USART接口与GPRS DTU连接,可对DTU进行配置并传输数据,另一个与GPS模块相连,用来获取精确到秒的时间信息。

无线通讯模块采用成都众山科技ZSD2110 GPRS DTU。ZSD2110是一款使用GPRS进行无线数据传输的终端设备,支持透明数据传输和用户自由控制传输模式,本系统中采用透明数据传输模式,不用关系复杂的网络协议,通过全透明串行口,就可进行无线数据收发,可大大简化单片机软件程序的设计。GPS授时模块采用Garmin的GPS15XL,它是12通道的GPS接收机,精密授时类型精度可达±50纳秒(典型值);具有串行端口,输出为RS232,输入可为RS232或者具有RS232极性的TTL电平,波特率从300~38400可选,默认为4800。可输出NMEA0183 2.0/3.0的ASCII码语句/Garmin二进制格式信息。非常适合应用于车辆导航、海事导航、电力系统校时等。由于DTU和GPS模块都是通过串行口与单片机连接,接口比较简单,需特别说明的是单片机与FPGA之间的数据通信接口电路。单片机PIC18F8520需通过其EMI接口从FPGA获取故障波形数据和时标信息。由于PIC18F8520的EMI接口中16bit数据线和低16bit的地址线共用,与FPGA之间不能直接相连,接口连接如图3所示。

故障定位装置的程序设计

故障定位装置的程序设计包括FPGA的内部逻辑设计和单片机的软件设计。

FPGA内部逻辑设计

FPGA的内部逻辑通过Altera公司的Quartus II集成环境,采用Verilog HDL硬件描述语言开发设计,分为以下几个模块。

(1)时钟信号生成模块:将50MHz的输入时钟通过计数器分频得到需要的时标标定电路的时钟信号、ADC转换时钟信号等系统需要的各种频率的时钟信号。

评论