基于FPGA的PPM系统设计与实现

—— 在满足性能需求的情况下消耗较少的逻辑资源

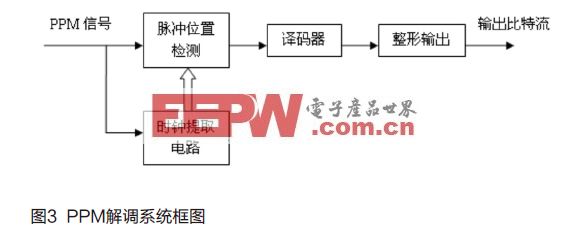

PPM系统实现及时序仿真

Verilog编码及原理图

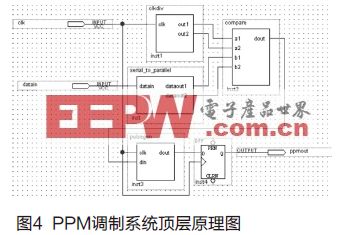

根据上述PPM系统的设计思想,基于FPGA的硬线逻辑特性,对各个功能模块进行Verilog编码来实现,并在顶层利用原理图输入的方式完成整机互联。而其中又以窄脉冲成型、为防止信号出现毛刺所作的整形电路、脉冲位置检测电路等为相对重要的模块。

调制系统的顶层原理图如图4所示。

其中窄脉冲成型模块性能的好坏影响着PPM脉冲对邻近信道的干扰情况,在设计该模块时可用触发器与附加逻辑来做脉冲成型滤波,较为简洁,其源代码如下:

/*to generate the narrow pulse*/

module pulsegen (clk,din,dout) ;

input clk,din;

output dout;

reg temp;

assign dout=(~temp)& din;

always @ (posedge clk)

begin

temp<=din;

end

endmodule

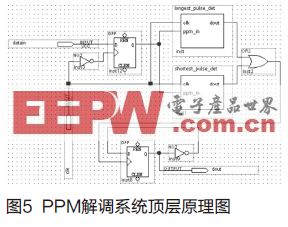

解调系统的顶层原理图如图5所示,最长脉冲位置检测模块和最短脉冲位置检测模块统一由时钟的上升沿触发,起到了良好的同步作用。

其中最短脉冲位置检测模块相对更为重要,需要精确地移位两个时钟周期,可用串行移位寄存器实现,其源代码如下:

fpga相关文章:fpga是什么

分频器相关文章:分频器原理

评论