基于CPLD内部的反向器实现振荡器应用

振荡器实现

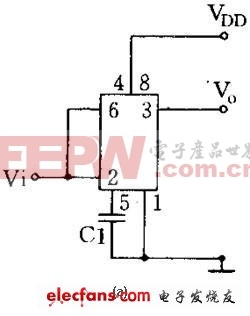

本文引用地址:http://www.eepw.com.cn/article/113013.htm利用CPLD内部的施密特触发器使输入波形得到校正,再加上反向器反向和外部RC实现振荡器,只需要在使用CPLD的任意两个I/O PIN引脚(当然从CPLD内部原理来看最好是使用相邻的两个PIN引脚,会减小CPLD内部资源的占用)。其中一个PIN 引脚串入电阻,外接一个对地电容,当内部的A点为高电平时,PIN1会通过R1对C1充电,由于电容的电压不可越变,电压是对电流的积分,所以电压会逐渐上升,当电平上升至0.5 × VCCIO,CPLD施密特触发器才认为是高电平,再经过内部的反向器会反向,所以A 点会变成低电平,这时C1 会通过R1逐渐放电,当放电电平低于0.5 x VCCIO时,反向器反向A点又变回高电平,这样反复的振荡就构成了一个稳定的振荡器时钟源(见表1)。

CPLD实现代码

本设计使用VHDL语言,选用XILINX 公司的COOLRUNNER-II系列的CPLD器件, 基于0.18nm CMOS CPLD, 3.8ns PIN-to-PIN延时,快速JTAG下载,2个bank,具体实现见代码列表。

振荡器应用

上述代码通过XILINX的编译综合器后,会产生一个可下载档案,此档案可以通过JTAG直接下载到芯片中使用,由于代码示例的为一个实时振荡器,也就是只有芯片上电,振荡器部分会一直工作,对于用于电源管理的嵌入式产品设计,由于一直振荡带来额外的电功耗损耗,功耗的损耗和振荡的频率是相关的,当频率越高时,功耗越大。所以,设计还可以再被优化使用。比如,当符合什么条件时振荡器才开始振荡,或者达到什么条件时振荡器停止振荡,这样灵活的优化设计会给产品带来更多的附加价值,延长电池的使用寿命。

振荡器的振荡频率是通过外部引脚的电阻和电容来调整的,当电阻越小,电容越小时,振荡的频率就很高。当电阻很大时,电容也变大,振荡的频率就会变低。振荡器的精度取决于外面电阻和电容的精度,电阻的精度以现在工艺可以做到1%的正负误差,电容可以选择5%的正负误差,高精度的电阻和电容会带来比较精准的振荡频率。

评论