加速IC测试工具开发进程

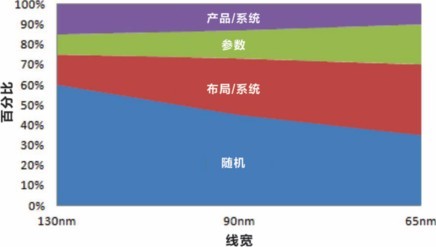

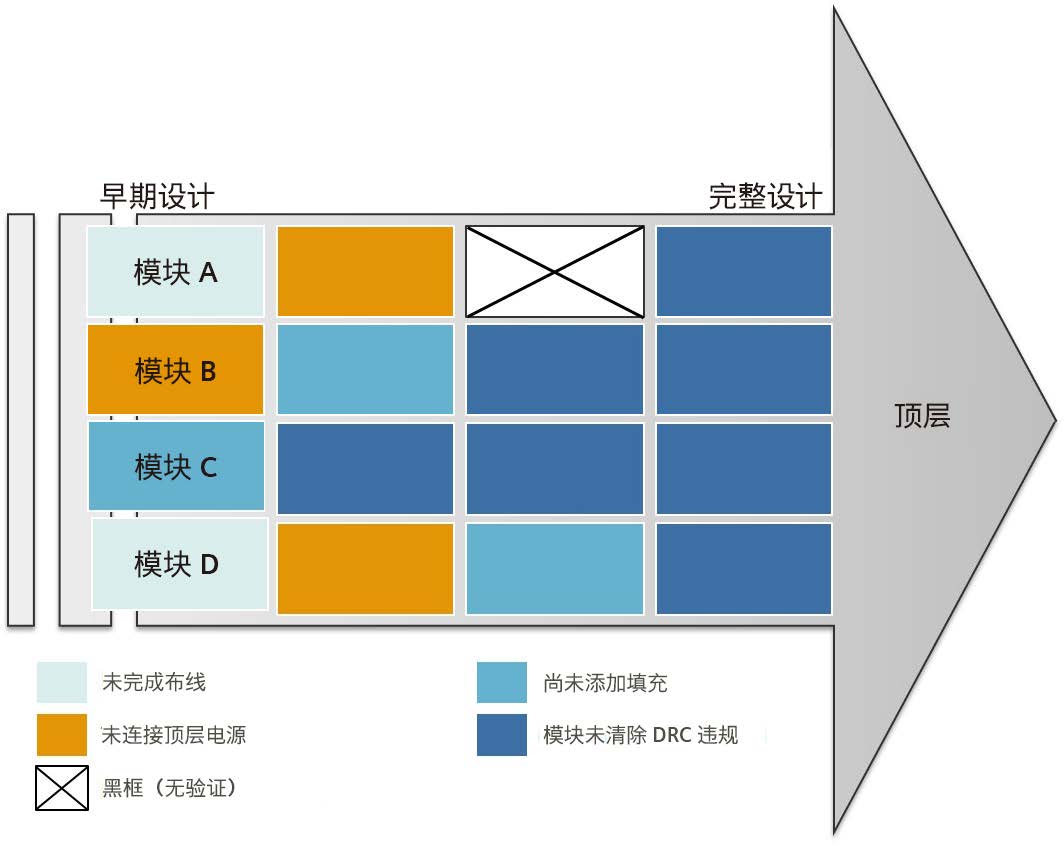

为了提高测试效率,对测试数据的压缩持续增长。据ITRS(半导体国际技术发展路线图)预测(图2),2010年的压缩需求比2009年翻番。

本文引用地址:http://www.eepw.com.cn/article/106766.htm

图2 测试数据量压缩的需求

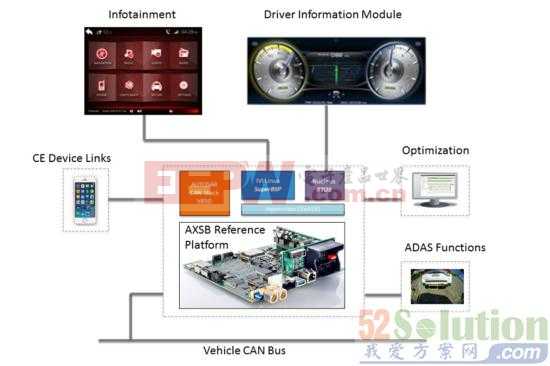

仔细分析,可见这是由多方面因素导致的。首先,测试项目的非常复杂,例如,芯片中的不同部分采用不同的测试工具,例如CPU核采用ATPG工具,内存需要内存BIST(内置自测试)工具和内存修理工具,I/O需要SERDES工具,PLL有PLL测试工具,ASIC需要逻辑BIST工具和边界扫描工具,另外,如何管理IP、工具、接口和相互作用等也是个问题。因此,这就有可能影响测试成本和上市时间。另外,纳米生产过程中也会出现一些光刻制造瑕疵(图3)。

图3 制造中的缺陷评估

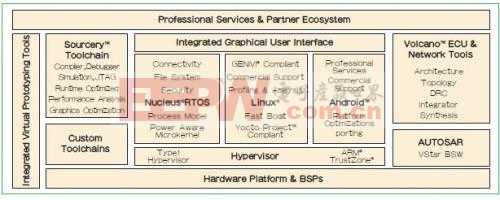

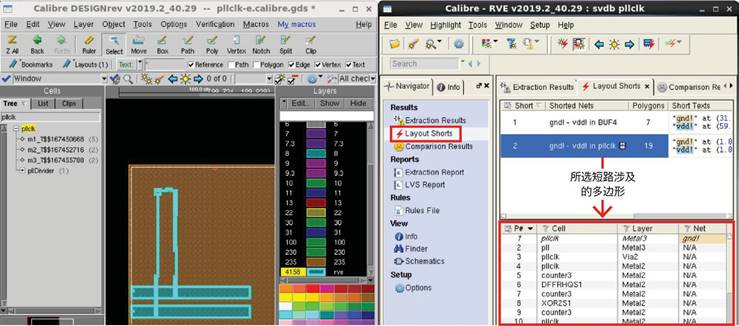

这些使测试更加复杂性,并有可能增加测试成本和延长上市时间。为了使客户应对更小的制程节点、更复杂、低功耗、混合信号SoC测试,Mentor推出了其嵌入式压缩和自动测试向量生成(ATPG)技术,与Mentor公司2009年8月收购的LogicVision公司的BIST技术结合,组合为Tessent。Tessent是最复杂的可测试设计(DFT)和芯片测试方案组合之一,它还包括LogicVision公司的SiliconInsight产品、Mentor的布线应用诊断工具和新发布的Tessent YieldInsight产品,可提供用于流片后(Post-silicon)的测试描述和产出分析。

评论